- The paper quantifies the trade-off between insertion loss and connectivity, showing that partially-connected architectures minimize hardware penalties with only minor capacity loss.

- It rigorously compares fully-flexible and partially-connected switching using capacity approximations and practical hardware models to assess spectral efficiency and energy consumption.

- The study provides actionable guidelines for implementing power-based antenna selection in fast-fading environments, optimizing performance for 5G/6G systems.

Reduced Switching Connectivity for Large Scale Antenna Selection: A Technical Analysis

Introduction and Motivation

Antenna Selection (AS) is a well-established architecture for reducing the hardware complexity, power consumption, and signal processing requirements in large-scale and massive MIMO systems. However, most prior work sidesteps the practical implications of the RF switching matrix that interfaces a limited number of RF chains with a much larger array of antennas. This paper systematically analyzes the quantitative effect of the RF switching architecture on system-level metrics, targeting massive MIMO downlink under TDD operation. The focus is not only on conventional fully-flexible switching matrices but critically on partially-connected switching architectures that offer reduced complexity and insertion loss while imposing combinatorial constraints on the AS policy.

RF Switching Architectures: Fully-Flexible and Partially-Connected

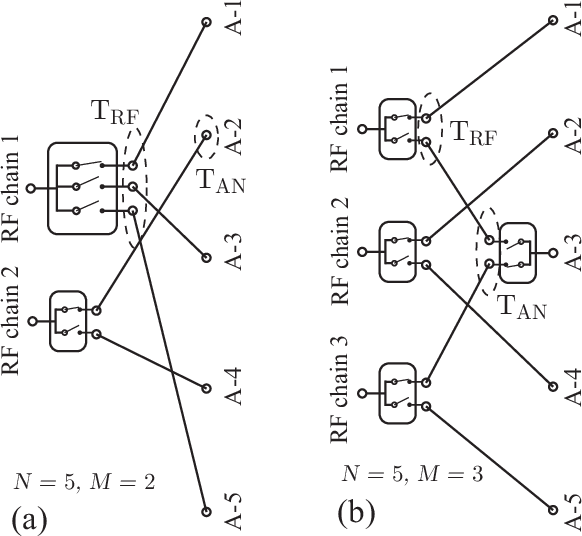

Fully-Flexible Architectures

Fully-flexible switching provides unconstrained connectivity between any RF chain and any antenna element, as illustrated in Figure 1. These designs can be realized using high-port-count switching matrices (e.g., cascaded SPXT switches), which, in the ideal case, allow an arbitrary subset of M antennas from N candidates to be selected. While this guarantees maximal instantaneous sum capacity (assuming optimal AS policy), it incurs substantial insertion loss (typically $2$–$3$ dB for realistic switch models and large N), increased hardware complexity, and significant power dissipation.

Figure 1: Block diagrams of fully-flexible architectures—a conventional 4×8 full-connectivity switching matrix and a minimum-connection alternative with the same flexibility.

Key architectural trade-offs include:

- Full Flexibility with Maximum Connectivity: Each RF chain connects to every antenna via the switching network, maximizing selection versatility but leading to the largest number of internal switch stages and highest insertion loss.

- Full Flexibility with Minimum Connectivity/Insertion Loss: Optimizing the switch design to reduce either the number of connections or insertion loss may paradoxically not coincide—the paper establishes that minimizing connectivity does not always minimize insertion loss due to non-monotonic loss increments with switch port count.

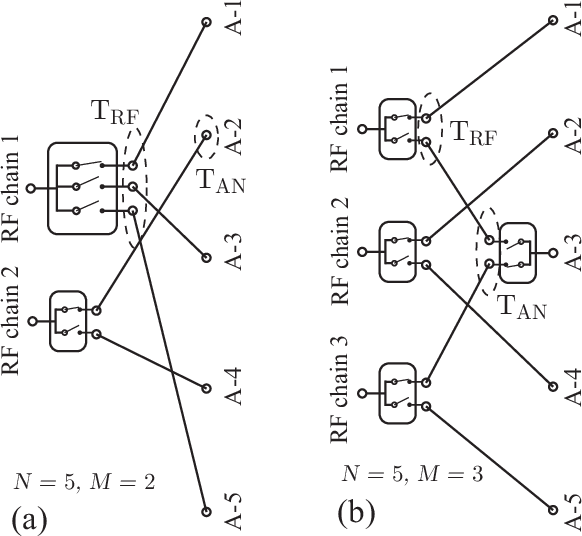

Partially-Connected Architectures

Partially-connected architectures directly address the aforementioned drawbacks by statically restricting the allowable antenna-to-RF-chain connections. A canonical implementation connects each RF chain to a distinct subarray (Figure 2), significantly reducing switch count and attainable insertion loss (e.g., $0.5$ dB versus >2 dB for N=128, M=64). However, this imposes combinatorial constraints that reduce the set of feasible antenna groupings, causing a provable but typically limited (for large N) ergodic sum capacity penalty.

Figure 2: Block diagrams for two partially-connected switching architectures with different ratios of antennas to RF chains.

Notably, the reduction in insertion loss improves effective SNR, partially compensating for suboptimal antenna selection. The analysis rigorously quantifies these effects for practical hardware models and real procedural constraints (such as the use of power-based AS relying on instantaneous power measurements rather than full CSI).

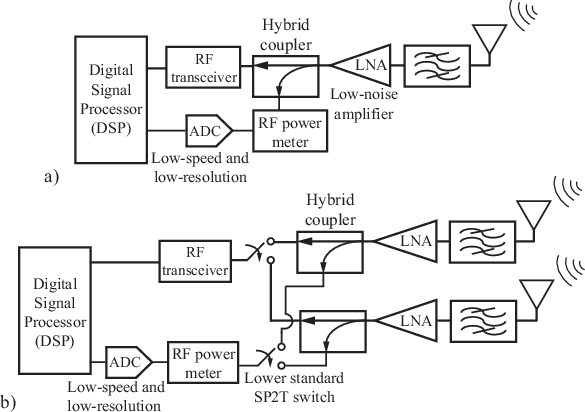

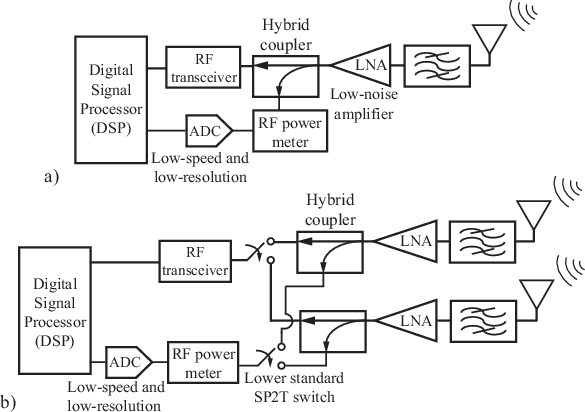

Hardware Implementation Considerations

Insertion loss dominates hardware penalization since transfer-function imbalance can be calibrated and port-to-port coupling is typically negligible (<−20 dB). Figure 3 exemplifies hardware designs for channel power acquisition, contrasting parallel per-antenna power meter chains with cost-optimized switchable subarrays.

Figure 3: Block diagrams of hardware implementations for per-antenna channel power measurement with varying cost/complexity.

These architectural decisions have broad implications for ADC/DAC counts, DSP datapath complexity, and overall power budget.

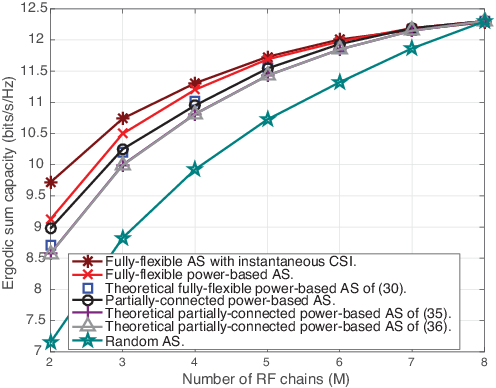

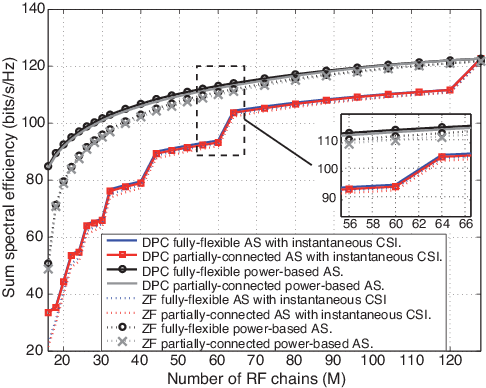

The analysis rigorously derives ergodic sum capacity approximations for both fully-flexible and partially-connected AS under independent Rayleigh fading, incorporating the impact of hardware-constrained AS feasibility sets and channel estimation overheads.

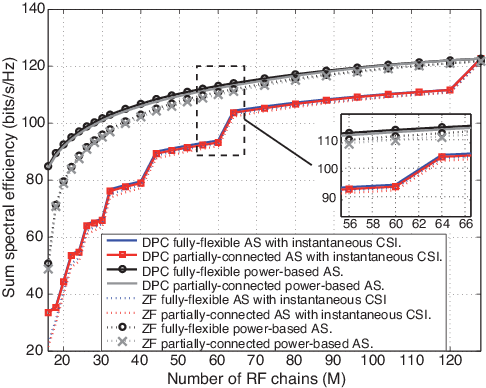

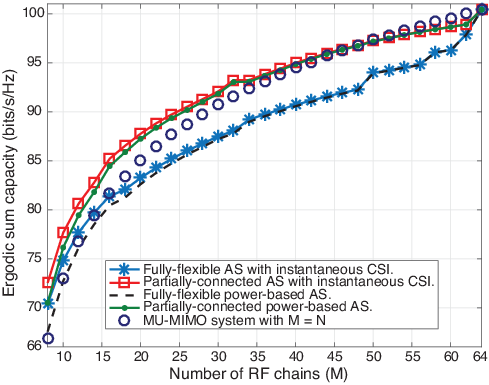

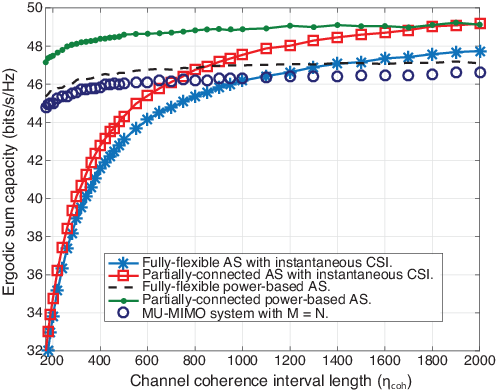

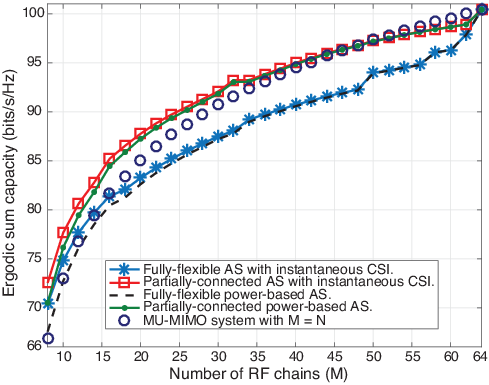

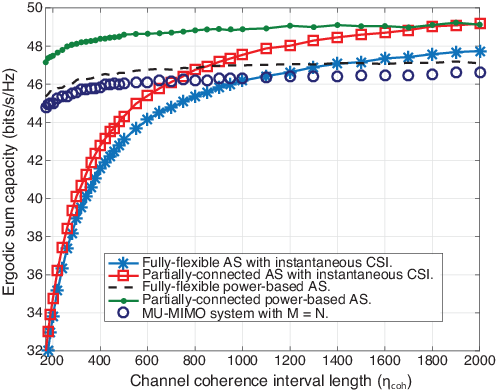

Figures 6–8 illustrate the effect of training overhead, insertion loss, and channel coherence on spectral efficiency and ergodic sum capacity. Power-based AS is near-optimal for systems with fast-fading channels and limited coherence intervals, highlighting the diminishing returns of full CSI acquisition and the advantages of using hardware-friendly norm-based selection.

Figure 5: Sum spectral efficiency versus active RF chains, capturing the effect of channel coherence and selection policy (DPC/ZF, instantaneous CSI versus power-based AS).

Figure 6: Ergodic sum capacity versus RF chains for DPC, showing the impact of switching insertion loss across architectures.

Figure 7: Ergodic sum capacity versus channel coherence interval for various switching architectures and selection strategies.

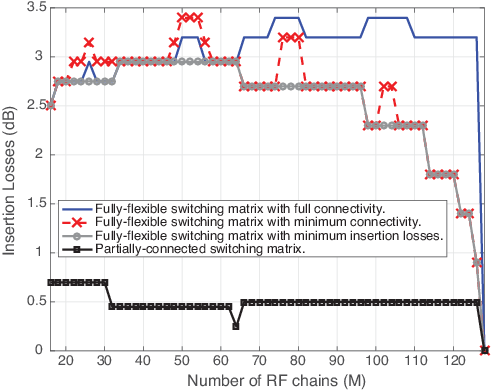

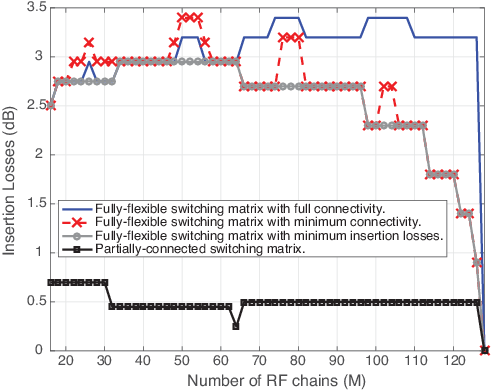

Insertion loss figures are explicitly plotted as a function of M (Figure 8), further quantifying the intrinsic benefit of partial connectivity in large-N systems.

Figure 8: Insertion losses versus RF chain count for representative switching architectures, demonstrating orders-of-magnitude reduction via partial connectivity.

Energy Efficiency and System-level Implications

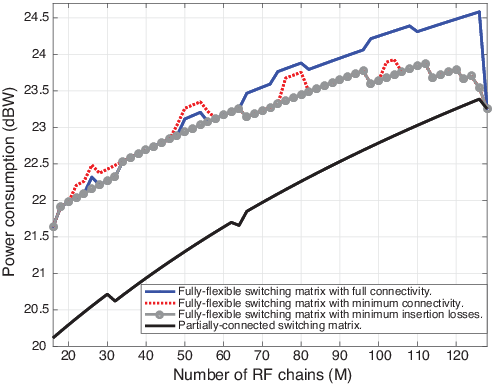

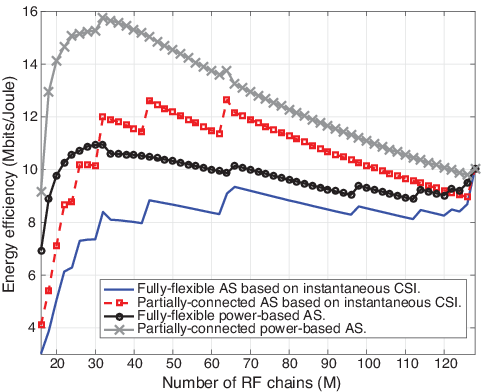

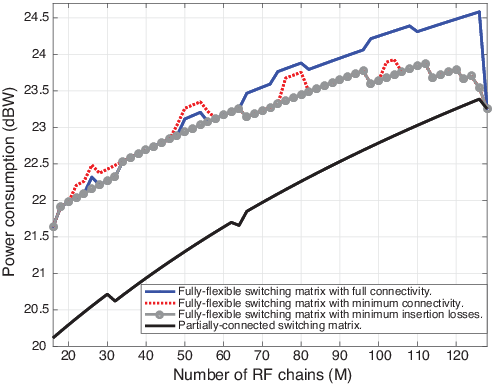

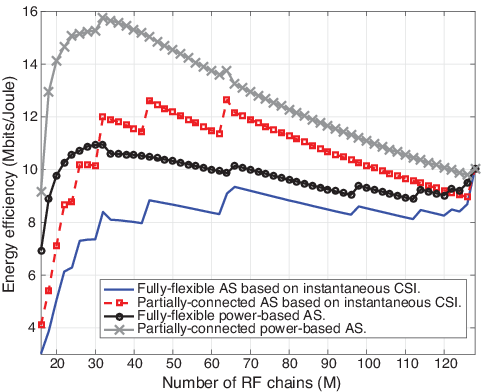

The quantitative impact of RF switching architecture on system energy efficiency is evaluated using a comprehensive power model, factoring in analog, digital (baseband), and interface domain costs. Figure 9 shows total system power as a function of M, with Figure 10 mapping the resulting energy efficiency.

Partially-connected AS maximizes system energy efficiency at a moderate number of RF chains (M≈32 for N=128), as it achieves a favorable trade-off between sum rate enhancement (before diminishing returns) and minimal hardware power penalties.

Figure 9: Total system power consumption versus RF chains, contrasting fully-flexible and partially-connected switching.

Figure 10: Energy efficiency versus number of RF chains for ZF precoding, showing optimal operational points for partially-connected switching.

These findings establish that, in the practical regime relevant to 5G/6G and beyond, the theoretical capacity penalty for partial connectivity is vastly outweighed by actual hardware and energy efficiency improvements.

Conclusion

The detailed analysis demonstrates that partially-connected RF switching architectures for AS in large-scale MIMO systems provide a compelling performance-versus-complexity trade-off. The reduction in insertion loss and system cost enabled by static or limited-connectivity switching delivers substantial improvements in effective SNR, system power consumption, and energy efficiency. Rigorous quantitative modeling shows that the combinatorial restrictions imposed by partial connectivity introduce only minor capacity loss—this is especially relevant as N grows large. For real-world deployments, power-based AS using these optimized switching matrices maximizes spectral and energy efficiency, particularly in mobility-constrained or fast-fading environments where CSI acquisition is a limiting factor.

The practical and theoretical framework provides clear guidelines for future research, including the extension to uplink-based power estimation, robustness to hardware nonidealities, and adaptation to advanced beam-switching topologies.