- The paper introduces the DeFT algorithm, which achieves deadlock-free routing using virtual network separation in 2.5D chiplet networks.

- The algorithm employs adaptive, congestion-aware vertical link selection to maintain fault tolerance and reduce latency during network faults.

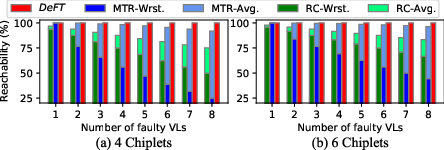

- Experimental evaluations show a 75% improvement in reachability with minimal hardware overhead, enhancing scalability and performance.

DeFT: A Deadlock-Free and Fault-Tolerant Routing Algorithm for 2.5D Chiplet Networks

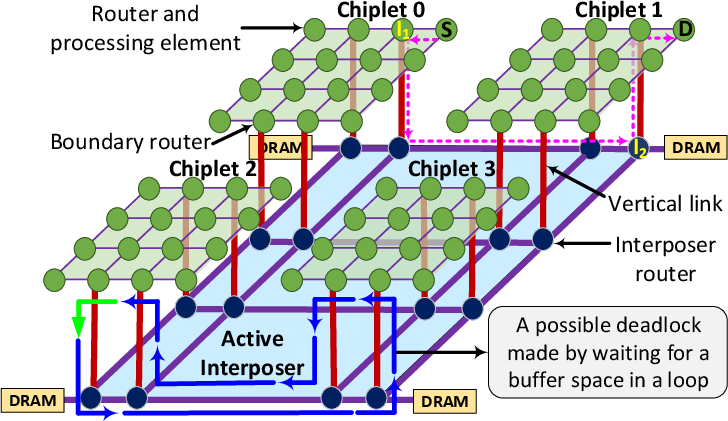

The "DeFT: A Deadlock-Free and Fault-Tolerant Routing Algorithm for 2.5D Chiplet Networks" paper introduces a routing algorithm named DeFT, innovatively addressing challenges in 2.5D integrated chiplet systems—specifically deadlock and fault tolerance related to vertical links (VLs) between chiplets and interposers.

Introduction and Overview

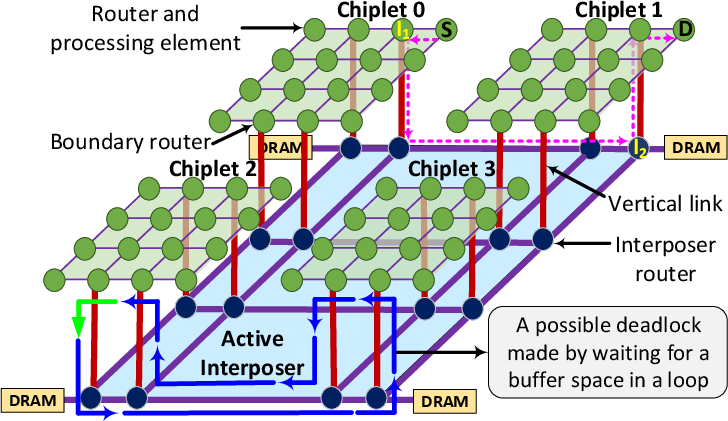

The demand for scalability in systems-on-chip (SoCs) is driving interest towards modular designs. 2.5D integration, where smaller chiplets communicate via an interposer, promises cost-effective scalability. Traditionally, deadlocks arise from cyclic dependencies in network packets, and conventional fault-tolerant routing methods from 2D and 3D systems do not directly apply to 2.5D networks due to architectural differences. DeFT addresses these by introducing a novel deadlock-free and fault-tolerant routing mechanism tailored for 2.5D chiplet networks, improving reachability and latency significantly over existing methods.

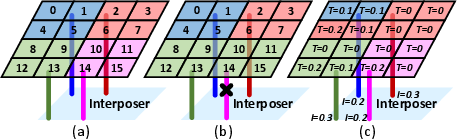

Figure 1: An abstract overview of the baseline 2.5D network with four chiplets on an active interposer.

Deadlock-Free Routing Strategy

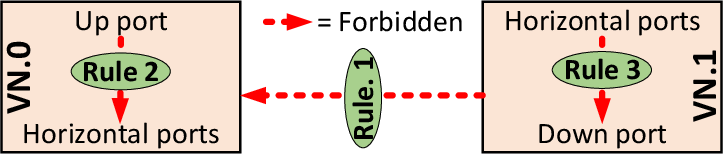

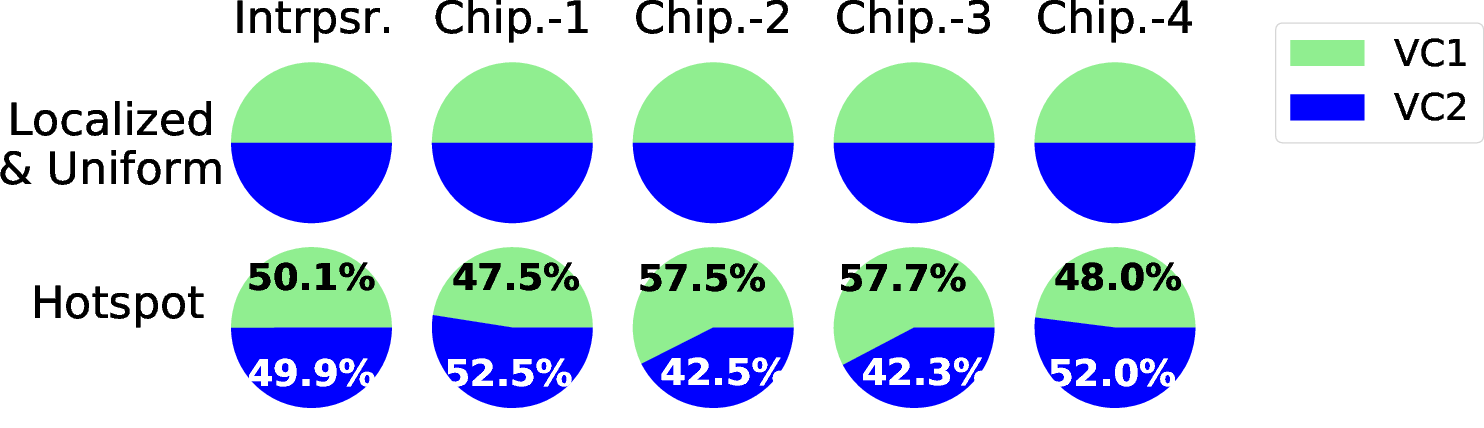

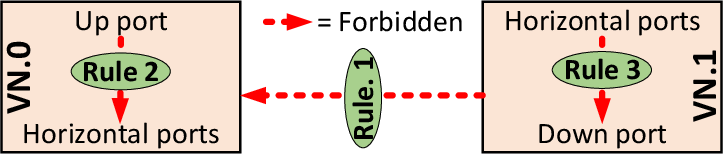

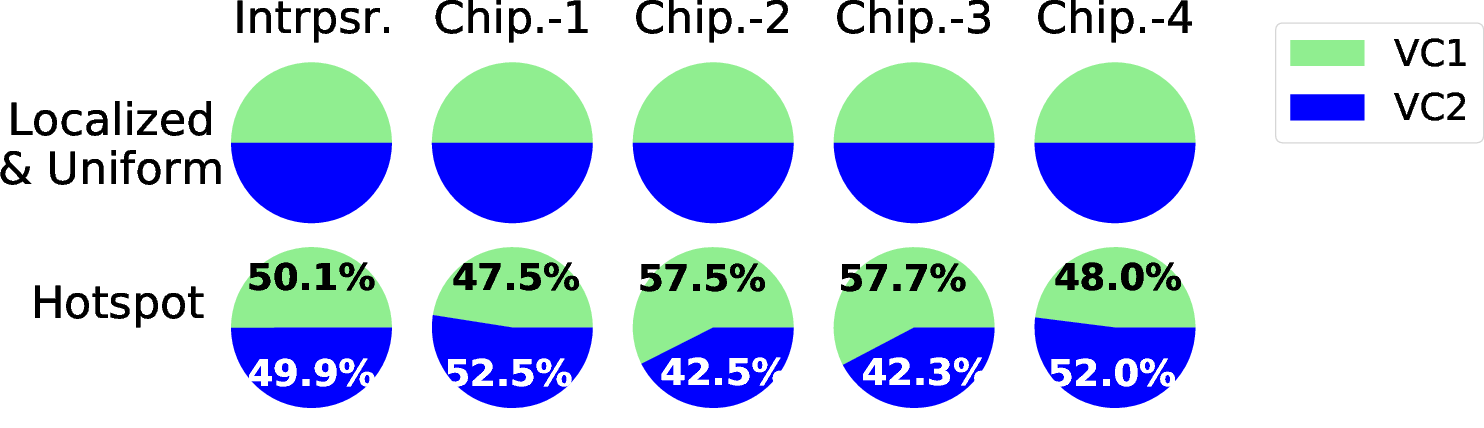

DeFT employs Virtual Networks (VN) and Virtual Channels (VC) for deadlock-freedom within the 2.5D network. VN separation is a key strategy, ensuring packets are distributed effectively across VCs with negligible hardware overhead while maintaining a balanced VC utilization. Three essential rules guide the VN utilization to ensure deadlock avoidance: prohibiting specific routing transitions between VN.0 and VN.1, and limiting certain routing maneuvers within each VN.

Figure 2: DeFT's rules for VN utilization and deadlock-freedom.

DeFT ensures module independence by not imposing constraints that would violate modular integration principles, differentiating it from the Modular Turn Restriction (MTR) and Remote Control (RC) algorithms. The VN assignment and deadlock-free routing rules optimize load distribution across the network, inherently balancing traffic and reducing latency during package routing between chiplets.

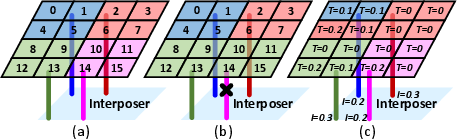

Fault-Tolerant and Adaptive VL Selection

DeFT uniquely addresses VL faults by implementing an adaptive and congestion-aware VL selection strategy. This strategy fine-tunes VL selection based on traffic profiles and fault scenarios, enhancing load distribution and minimizing congestion. The algorithm involves pre-analyzing optimal selections for VL configurations under various fault scenarios and storing them in lookup tables within routers. During runtime, this allows for swift adaptations to ensure ongoing fault tolerance and maintain network performance under different fault conditions.

Figure 3: Examples for a VL selection: (a) a fault-free distance-based selection (closest VL), (b) a distance-based selection in the presence of a VL fault, and (c) a good selection under non-uniform traffic.

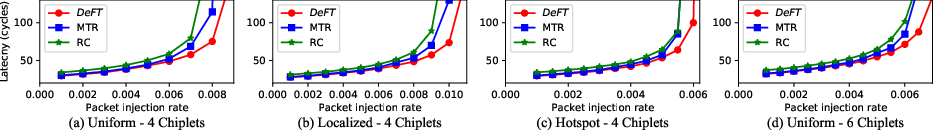

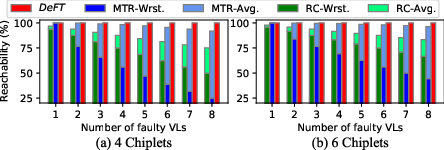

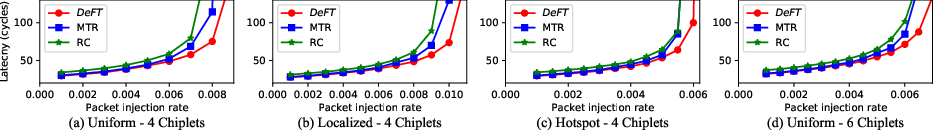

Experimental results highlight DeFT's superior performance across several synthetic and real-world application scenarios. DeFT achieves significant latency improvements and increased reachability under fault conditions compared to the MTR and RC algorithms.

Figure 4: Average latency comparison among DeFT, MTR, and RC routing algorithms when applied to the network shown in Fig. 1 and under (a) Uniform, (b) Localized, and (c) Hotspot synthetic traffic patterns. (d) shows the same but for 6 chiplets and Uniform traffic.

Under real-application traffic and synthetic traffic patterns, DeFT consistently offers lower latency, as demonstrated in various configurations and traffic patterns, improving the performance robustness of chiplet-interconnected systems.

Figure 5: VC utilization in DeFT under synthetic traffic.

Additionally, DeFT's ability to maintain full reachability amidst vertical link faults showcases its robustness—achieving a 75% improvement in network reachability with fault rates up to 25%.

Figure 6: Reachability in the presence of VL faults in a system with (a) 4 chiplets (total VLs=32), and (b) 6 chiplets (total VLs=48). Note that DeFT-Wrst. and DeFT-Avg. are the same (both shown by DeFT).

Resource Utilization and Efficiency

The hardware implementation of DeFT, analyzed using synthesis tools like Cadence Genus, shows that DeFT imposes less than 2% overhead in area and 1% overhead in power compared to state-of-the-art techniques. The minimal resource demands are primarily due to the efficient VN assignment logic and lookup tables for VL selection.

Conclusion

DeFT demonstrates a novel approach to routing in 2.5D chiplet networks by integrating deadlock-free, fault-tolerant principles with adaptive methodologies to manage traffic loads and routing faults effectively. This breakthrough offers practical scalability improvements in chiplet-based modular integration, presenting an adaptable and efficient routing strategy under diverse operational conditions. As future scenarios push the boundaries of chiplet designs, DeFT's methodology will remain pivotal in advancing the reliability and performance of 2.5D integrated systems.