- The paper introduces a 16-channel low-power SoC for extracting neural connectivity and facilitating phase-locked deep brain stimulation, providing a significant leap in closed-loop neuromodulation technology.

- Key advancements include precise analog front-end design, real-time neural connectivity processing, and energy-efficient stimulation, demonstrating >60% power savings compared to existing systems.

- In-vivo studies validated the SoC's robust phase and connectivity analysis, suggesting enhanced therapeutic potential for treating movement and psychiatric disorders.

16-Channel Low-Power Neural Connectivity Extraction and Phase-Locked DBS SoC

Introduction and Motivation

This work presents a 16-channel system-on-chip (SoC) for neural connectivity extraction and phase-locked deep brain stimulation (DBS), targeting the regulation of pathological brain states in neurological and psychiatric disorders. The SoC integrates low-noise multi-channel local field potential (LFP) recording, real-time extraction of instantaneous phase and cross-regional synchrony measures, and charge-balanced neurostimulation. The motivation stems from the limitations of conventional open-loop DBS, which can induce side effects and lack efficacy in network-based disorders. Phase-locked DBS, which delivers stimulation synchronized to ongoing neural oscillations, has demonstrated improved outcomes in movement disorders and is hypothesized to be beneficial for psychiatric and memory disorders by modulating abnormal connectivity.

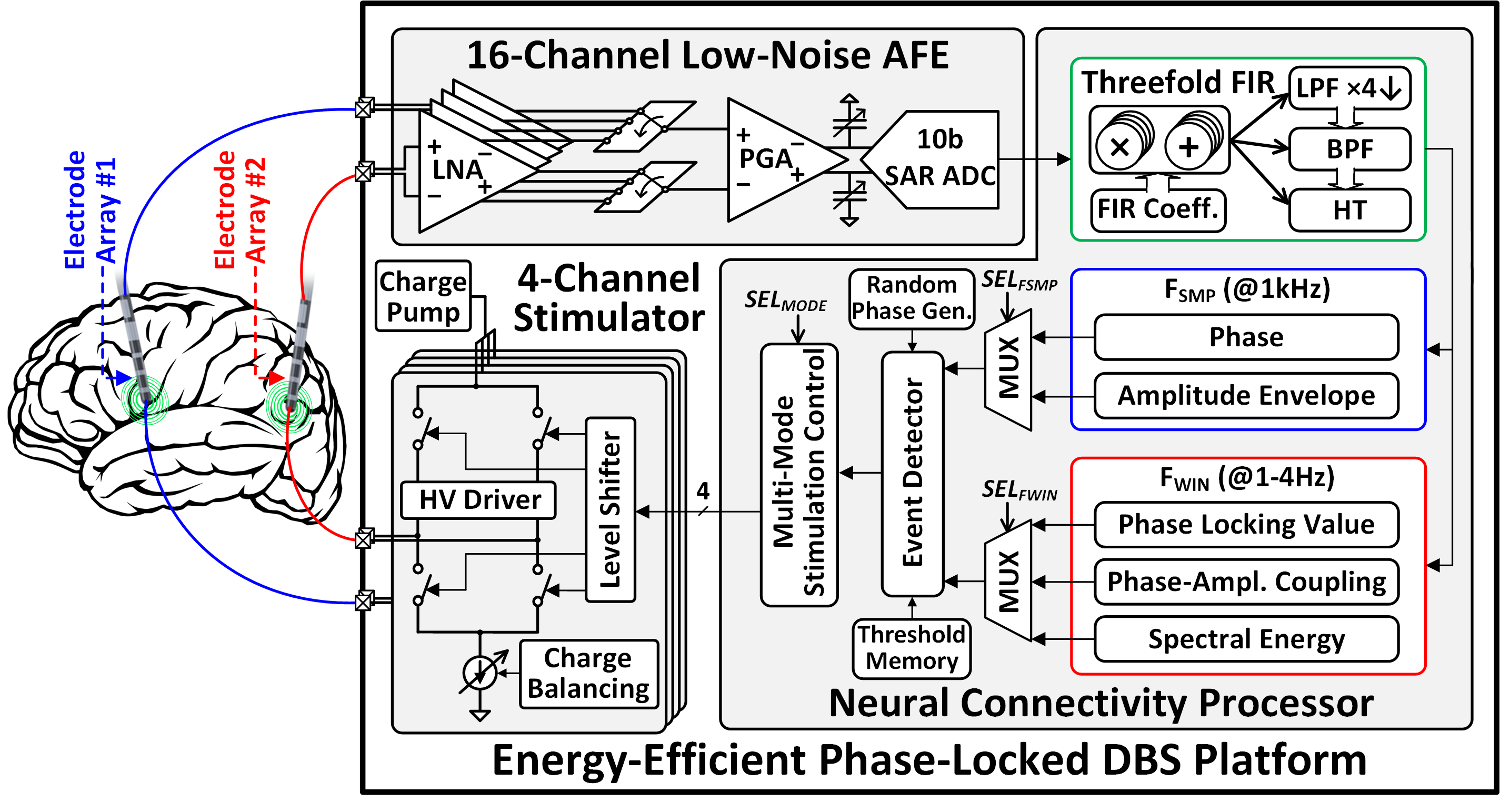

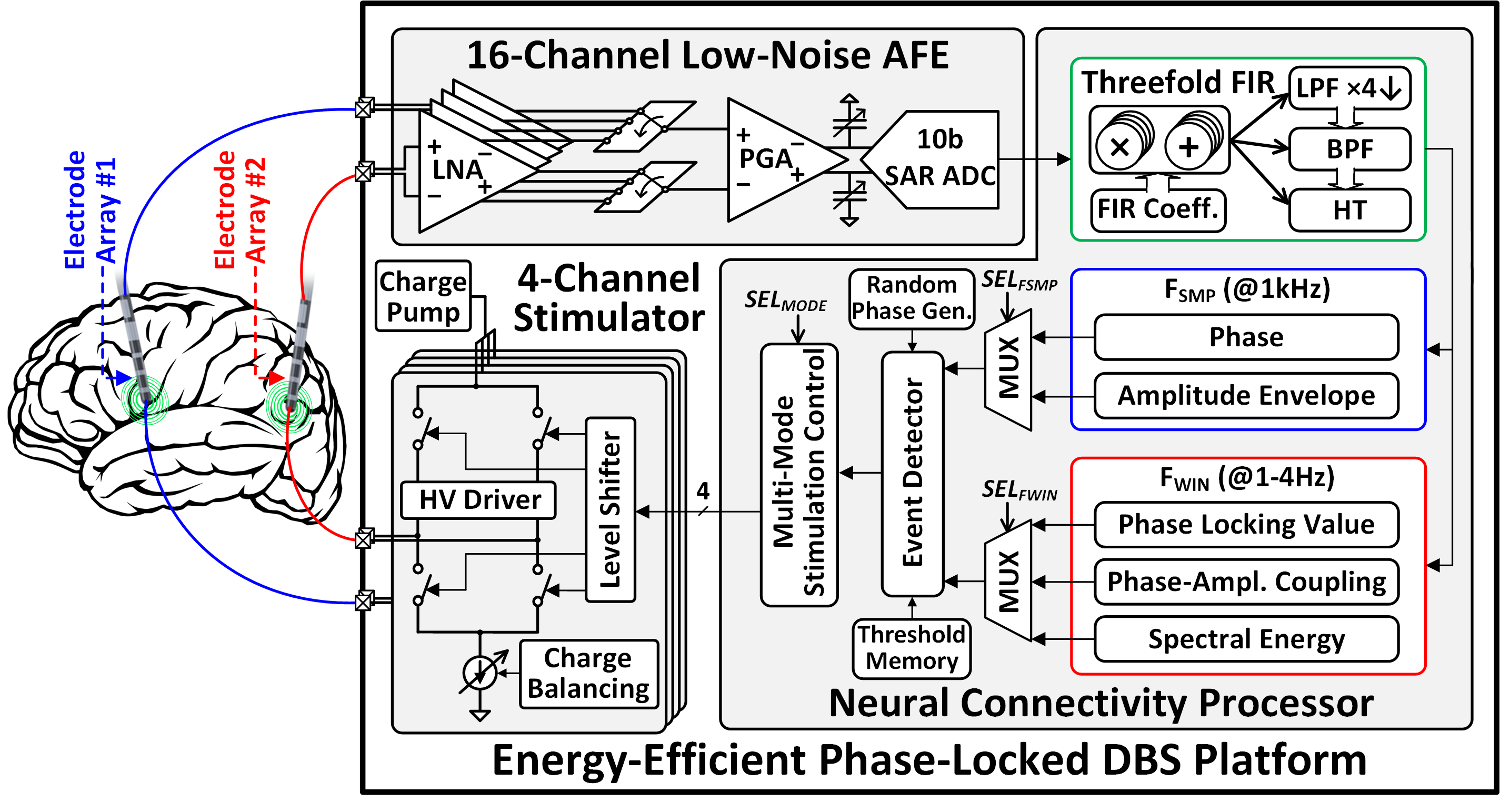

Figure 1: Architecture of the proposed 16-channel neural connectivity extraction and phase-locked DBS SoC.

System Architecture

The SoC architecture comprises three main subsystems: a 16-channel chopper-stabilized analog front-end (AFE), a neural connectivity processor, and a four-channel charge-balanced neurostimulator. The AFE records LFPs from multiple brain regions with precise gain matching, essential for accurate cross-regional connectivity analysis. The digitized signals are processed by a programmable finite impulse response (FIR) filter, which performs decimation, bandpass filtering, and Hilbert transform via hardware sharing. The feature extractor computes instantaneous phase, amplitude envelope, phase locking value (PLV), phase-amplitude coupling (PAC), and spectral energy (SE) in real time. Upon detection of pathological activity, the neurostimulator delivers biphasic pulses locked to specific phases of neural oscillations.

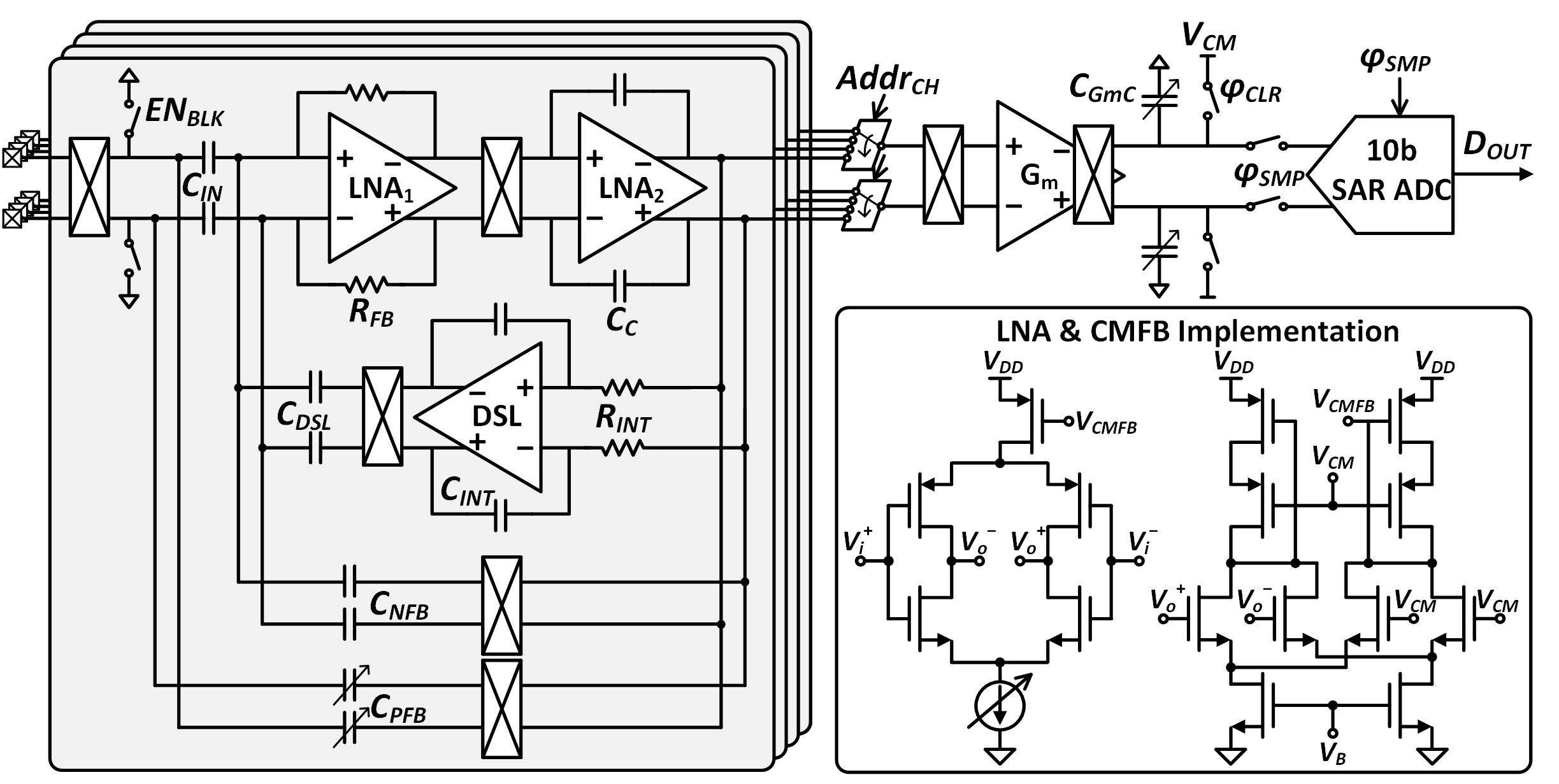

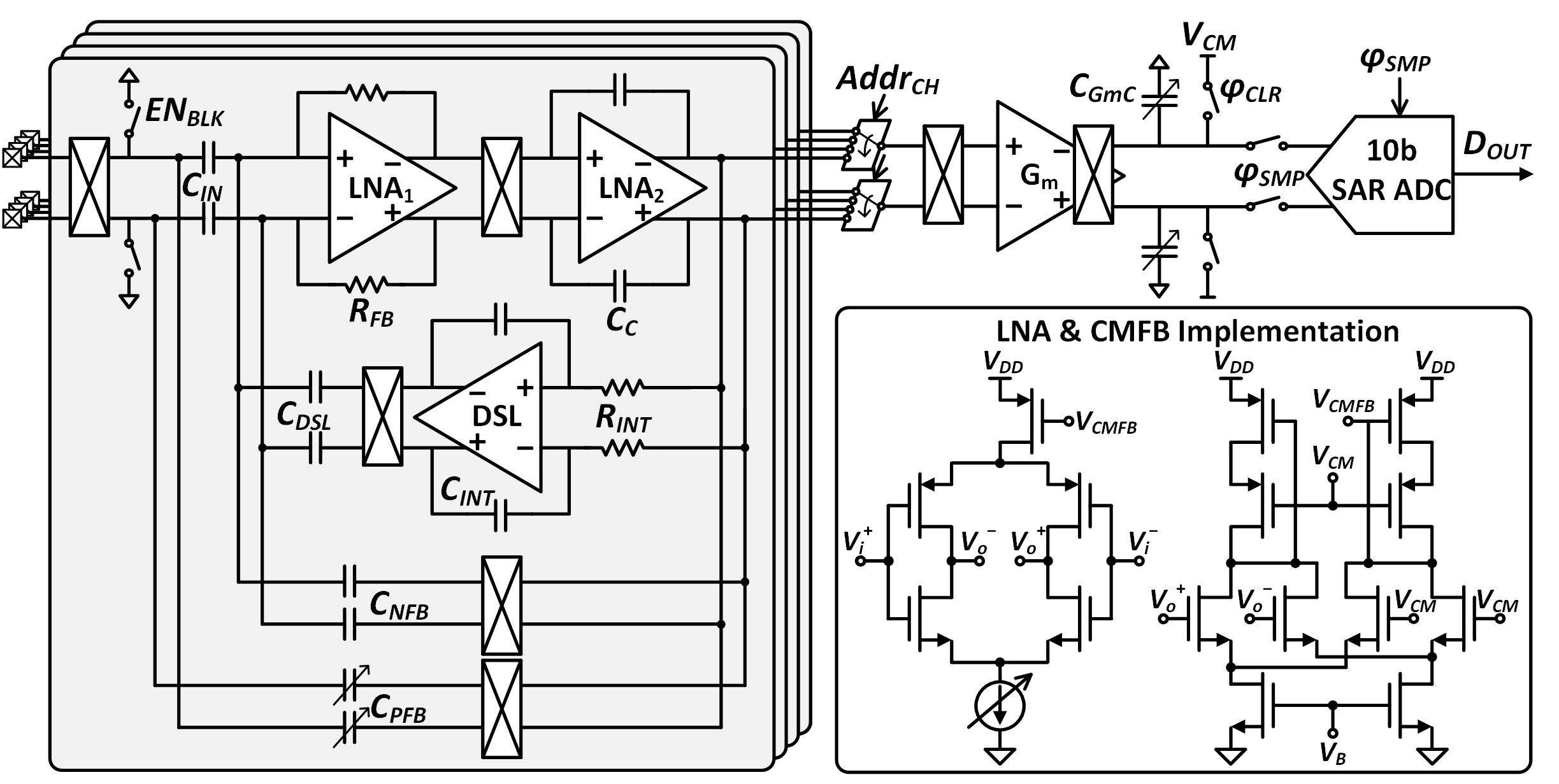

Figure 2: Circuit implementation of the 16-channel chopper-stabilized AFE.

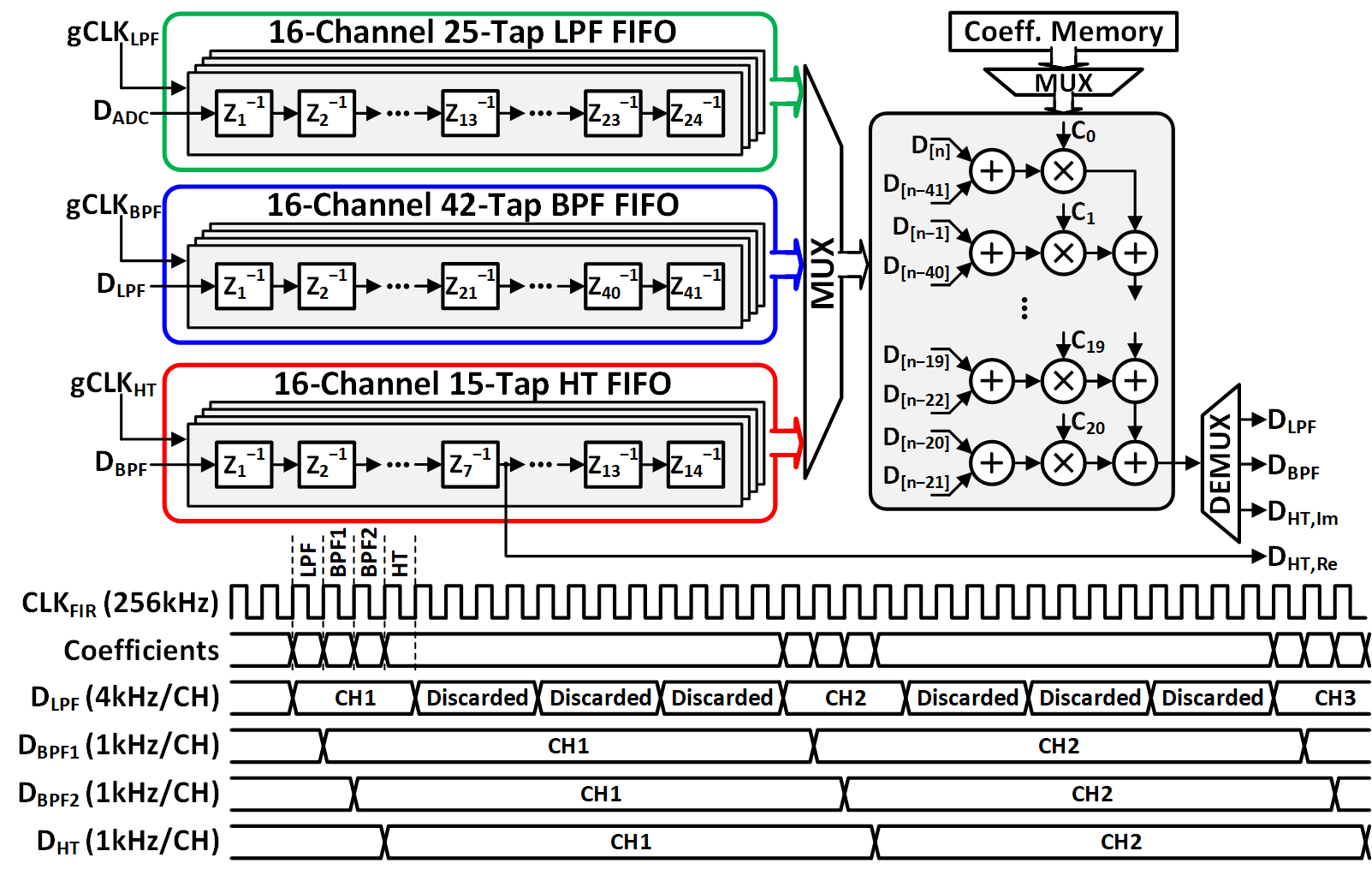

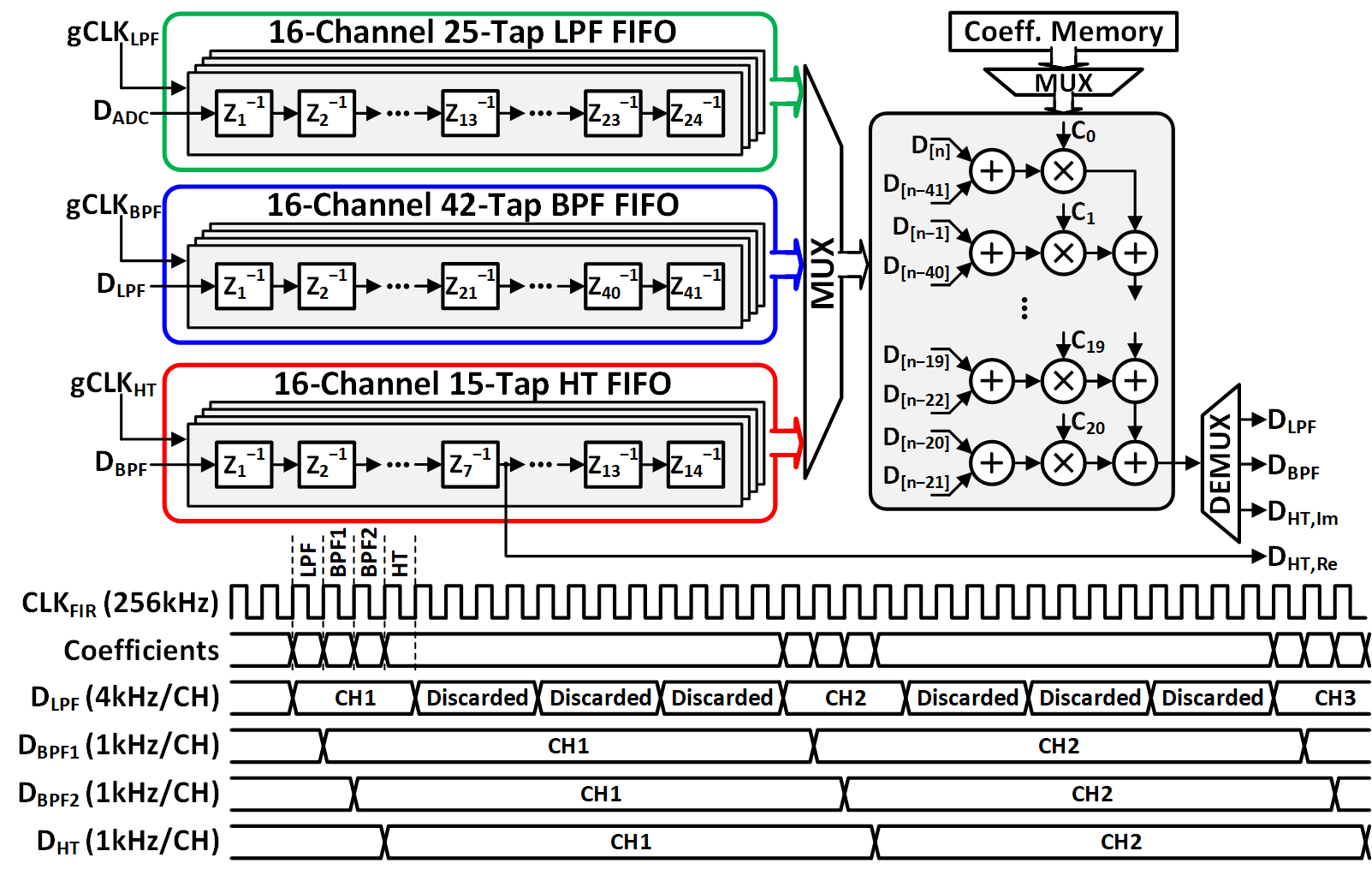

Figure 3: Programmable threefold FIR filter architecture and timing diagram.

Circuit Implementation

Analog Front-End

The AFE utilizes two-stage low-noise amplifiers (LNAs) with a current-reuse inverter topology and chopper stabilization to suppress flicker noise in the 1–500 Hz LFP band. A DC servo loop cancels electrode offsets, and a tunable positive feedback capacitor enhances input impedance. The 16-channel outputs are multiplexed into a programmable-gain integrator and digitized by a 10-bit SAR ADC. Precise gain matching (σ/mean<0.1%) across channels is achieved, which is critical for connectivity analysis. Blanking circuitry prevents amplifier saturation during stimulation by resetting the AFE input.

Neural Connectivity Processor

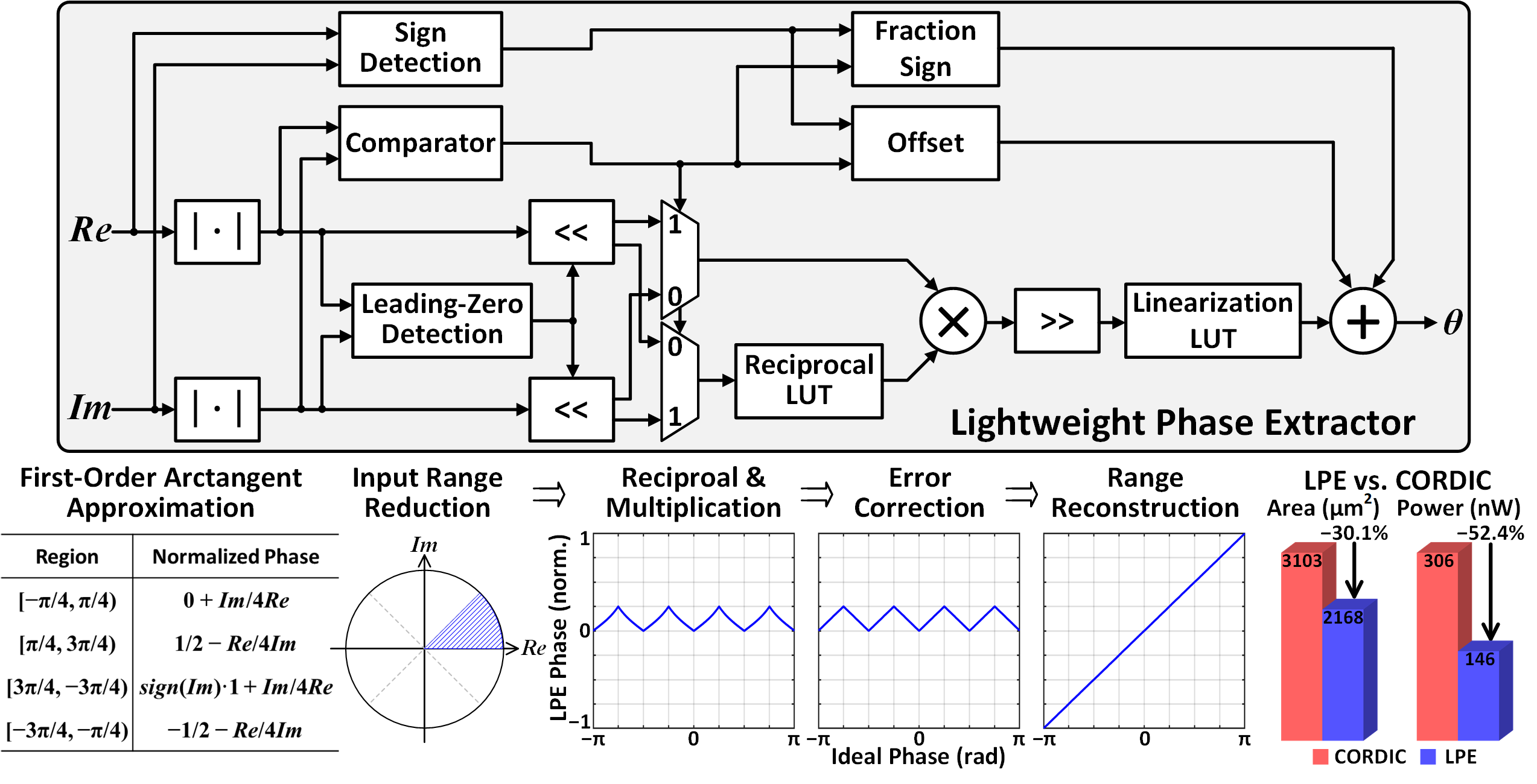

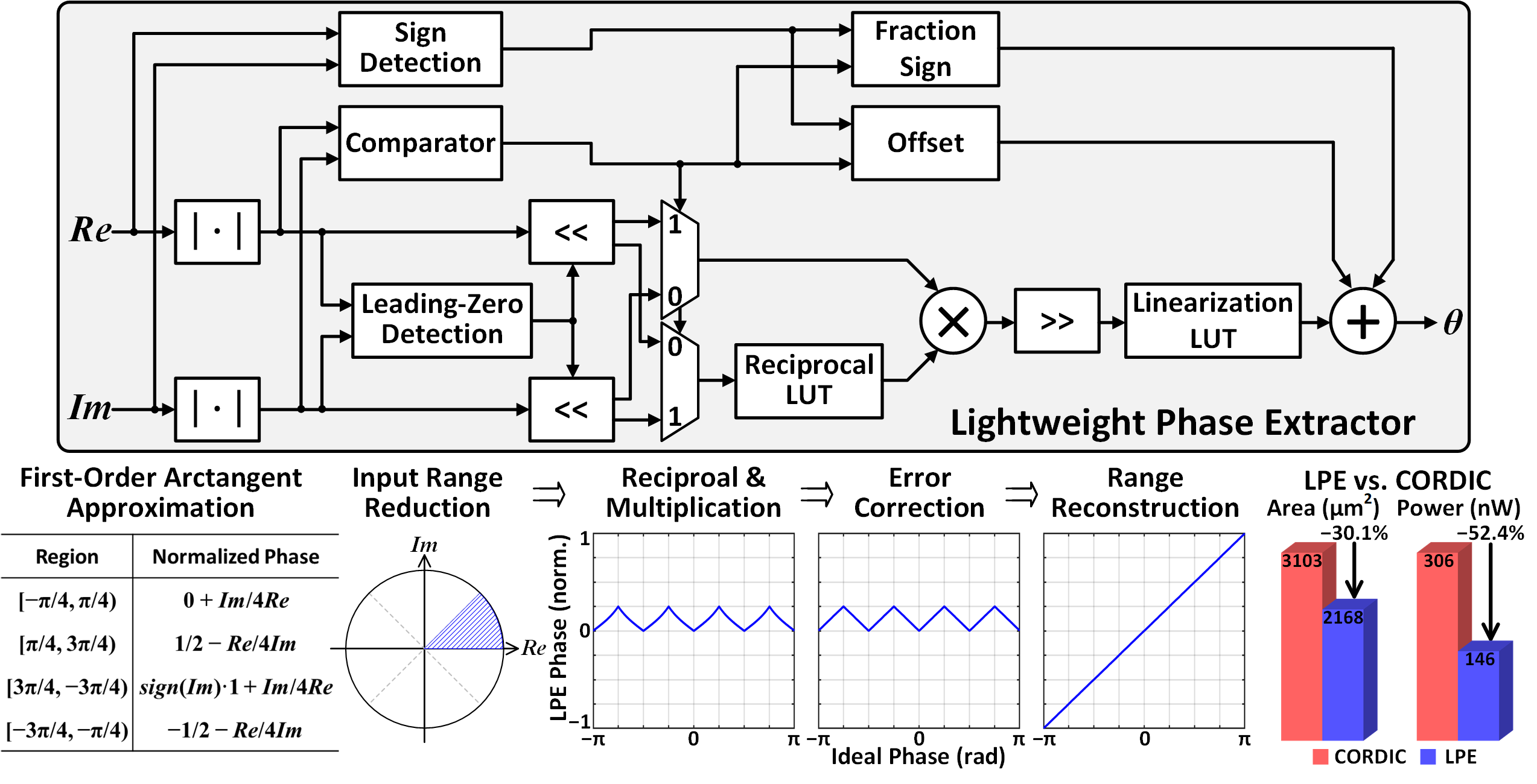

The FIR filter architecture shares multiplier-adder chains across three delay banks (LPF, BPF, HT), reducing area and dynamic power via clock and data gating. The Lightweight Phase Extractor (LPE) implements first-order Lagrange interpolation for phase extraction, using sign detection, magnitude comparison, reciprocal and linearization LUTs, and trigonometric periodicity identities. The LPE achieves last-bit accuracy with respect to infinite-precision arctangent, is 30.1% more area efficient, and consumes 52.4% less power than a 10-bit unrolled CORDIC.

Figure 4: Proposed LPE hardware and illustration of the underlying algorithm.

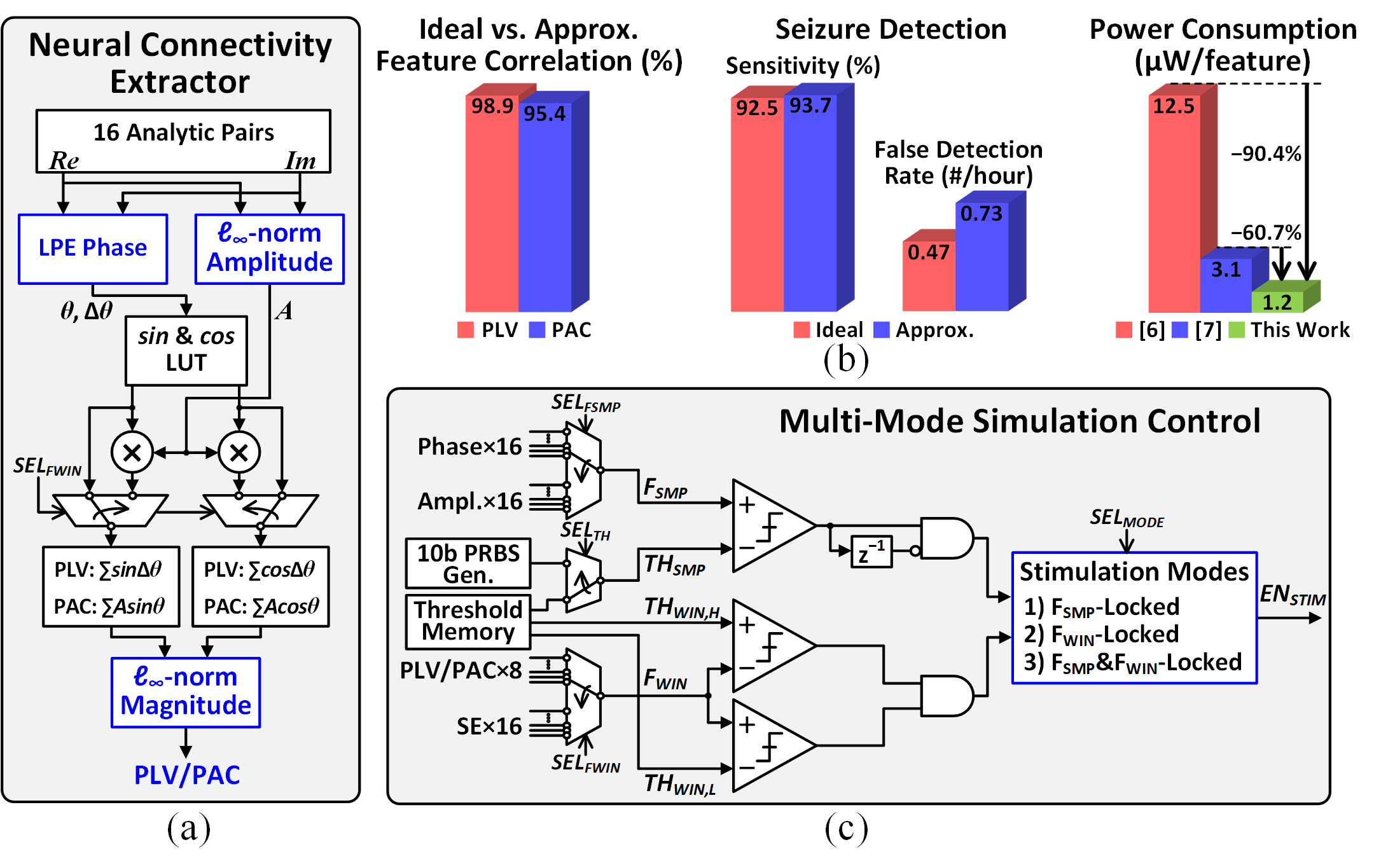

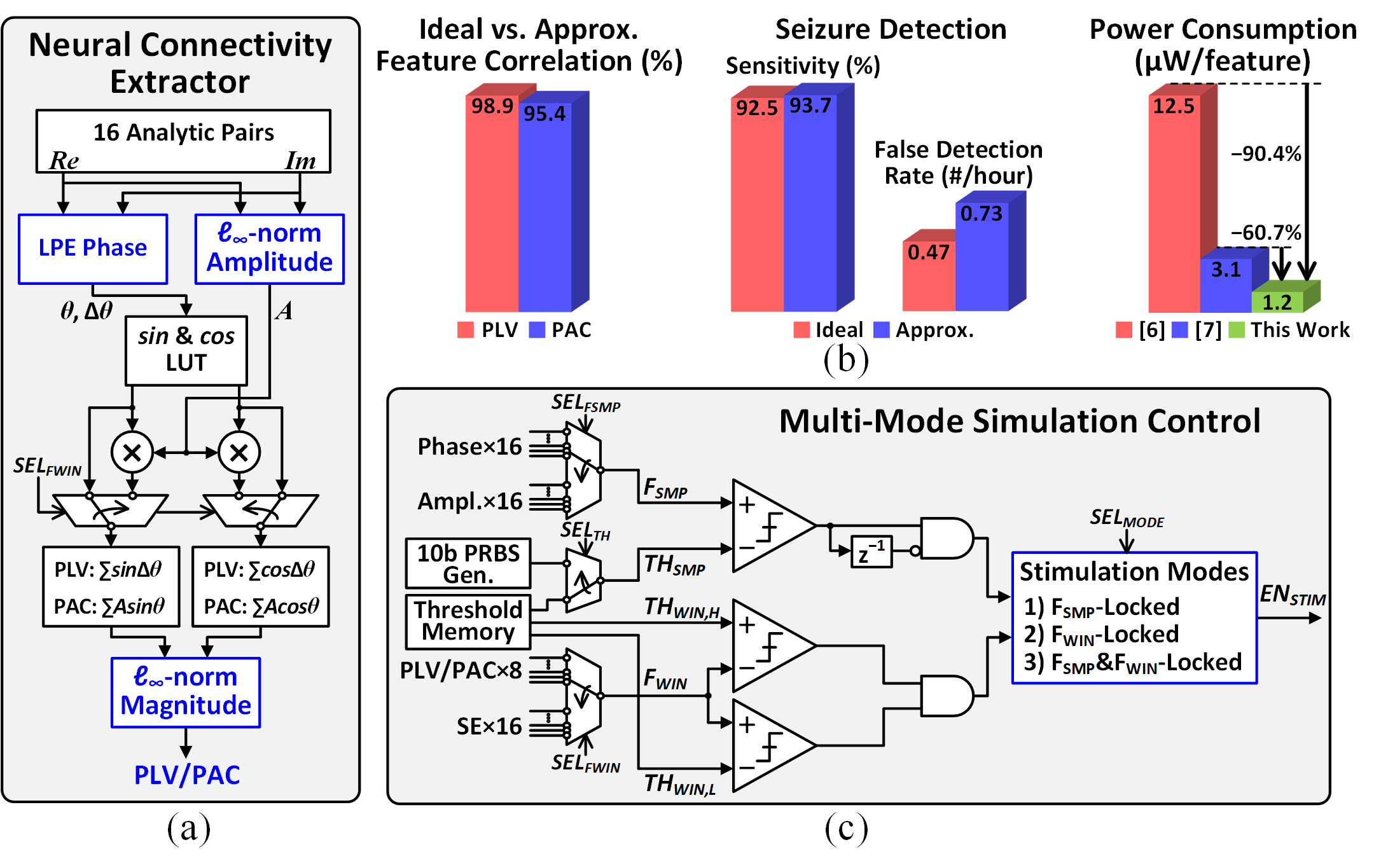

Figure 5: (a) Proposed neural connectivity extractor, (b) feature accuracy analysis and power comparison, and (c) multi-mode stimulation control.

The feature extractor approximates the complex Euclidean norm with the l∞-norm for amplitude envelope computation, validated to yield >95% correlation with ideal features and negligible impact on seizure detection performance. The processor can extract 8 PAC/PLVs, 16 phases, and 16 amplitude envelopes from 8 channel pairs at 9.69$\upmu$W, representing >60.7% power savings over CORDIC-based designs. Multi-mode stimulation control is supported, enabling phase-locked, connectivity-locked, or randomized stimulation via a PRBS threshold generator.

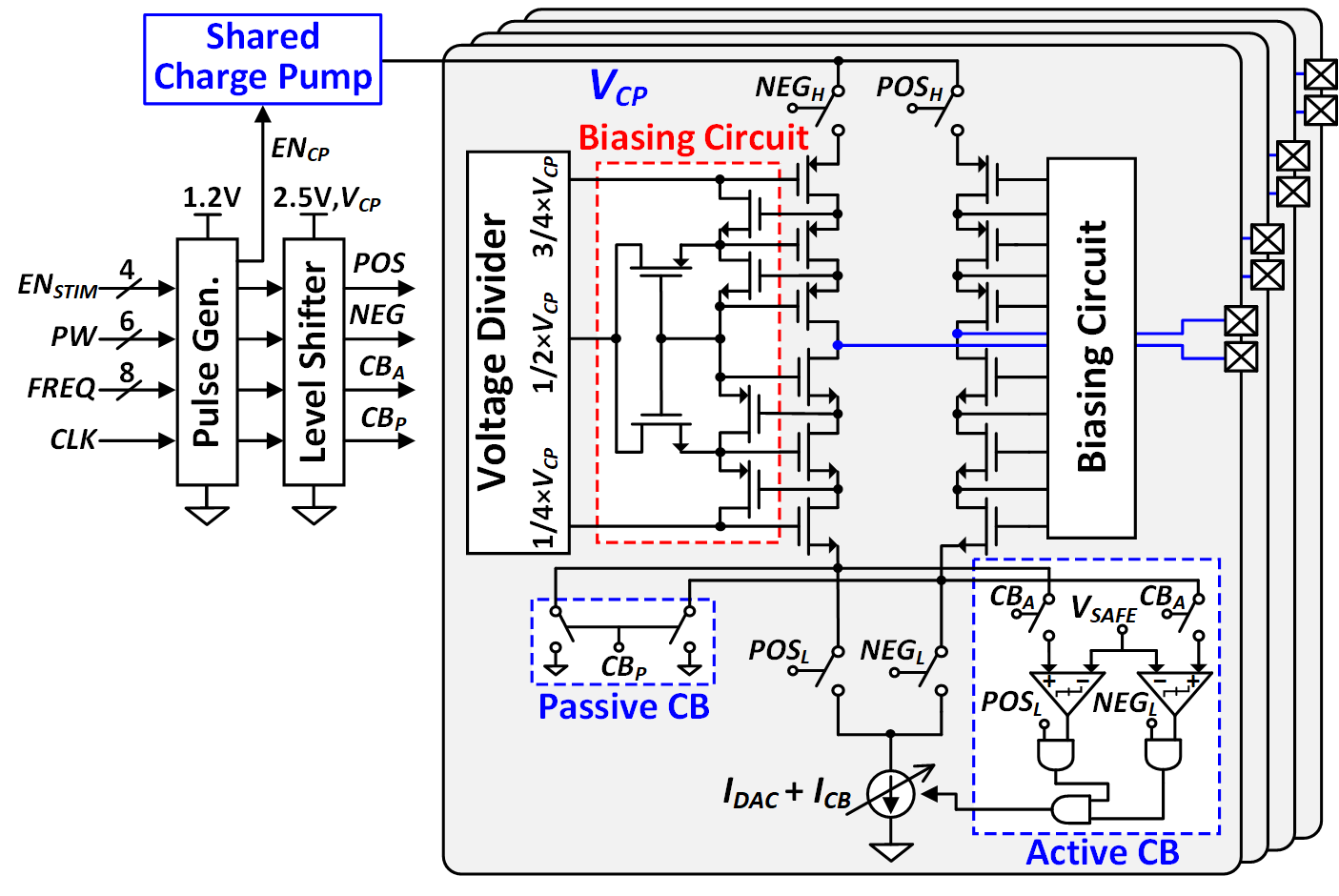

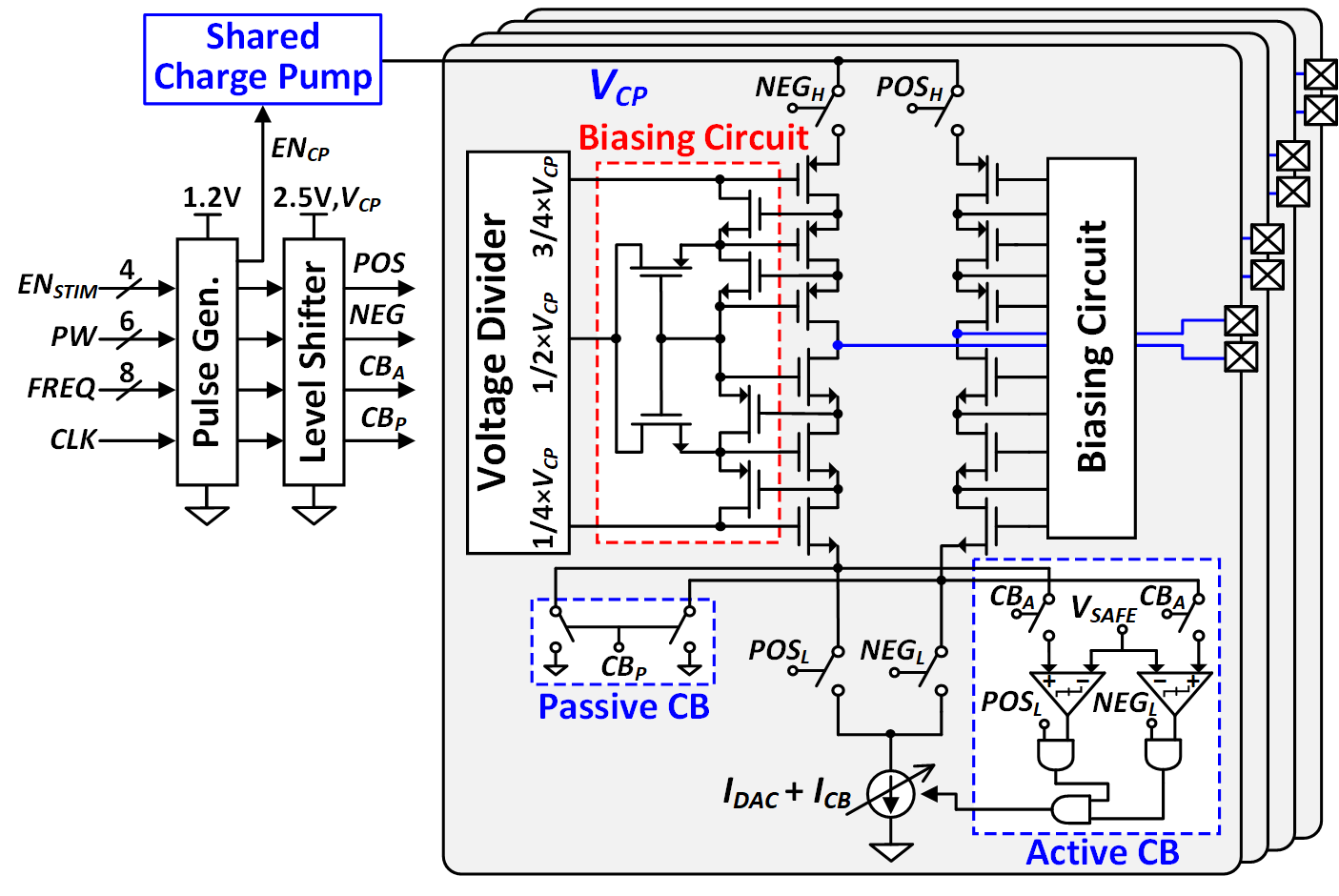

Neurostimulator

The four-channel neurostimulator employs a high-voltage compliant stacked architecture with an H-bridge current driver and active charge balancing. Biphasic pulses are precisely matched, and residual electrode-tissue interface voltages are kept below ±VSAFE, with passive discharging for any remaining charge.

Figure 6: High-voltage compliant charge-balanced neurostimulator.

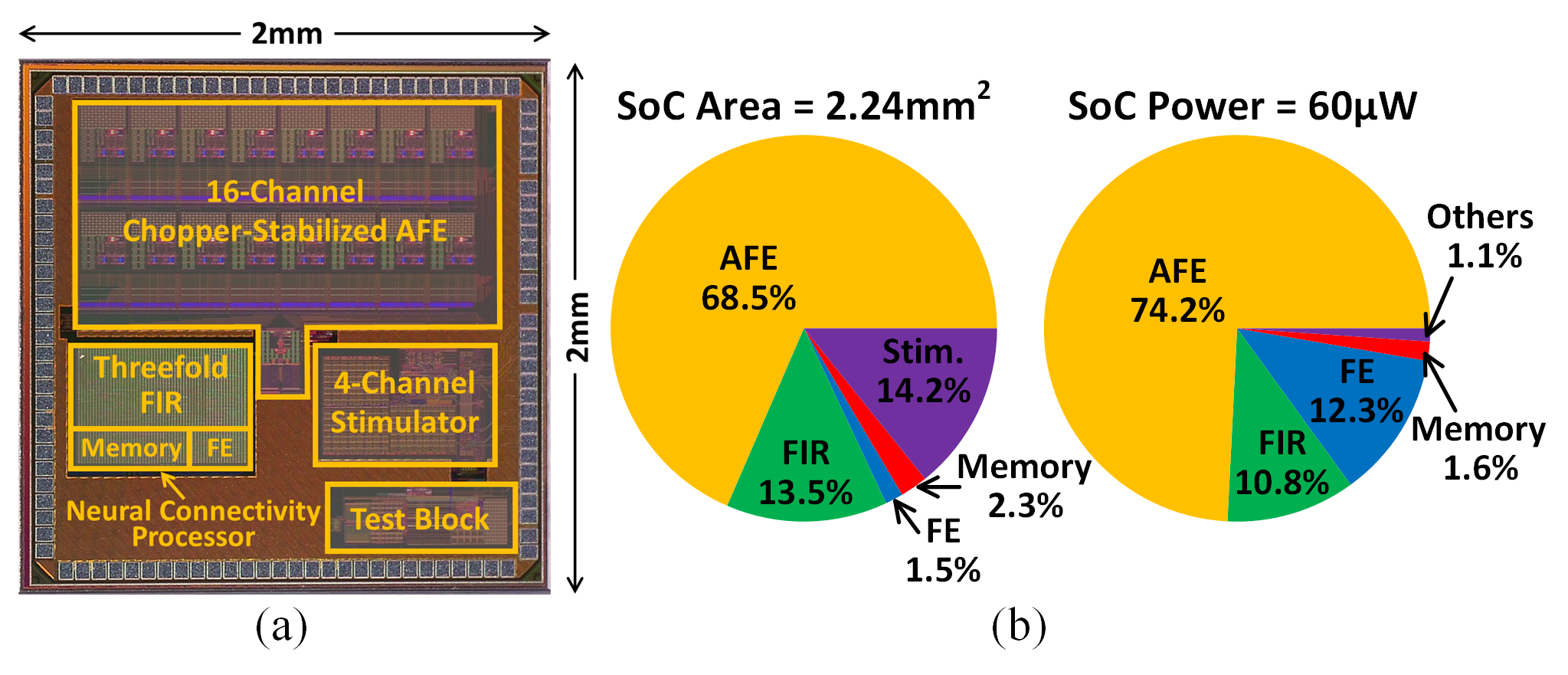

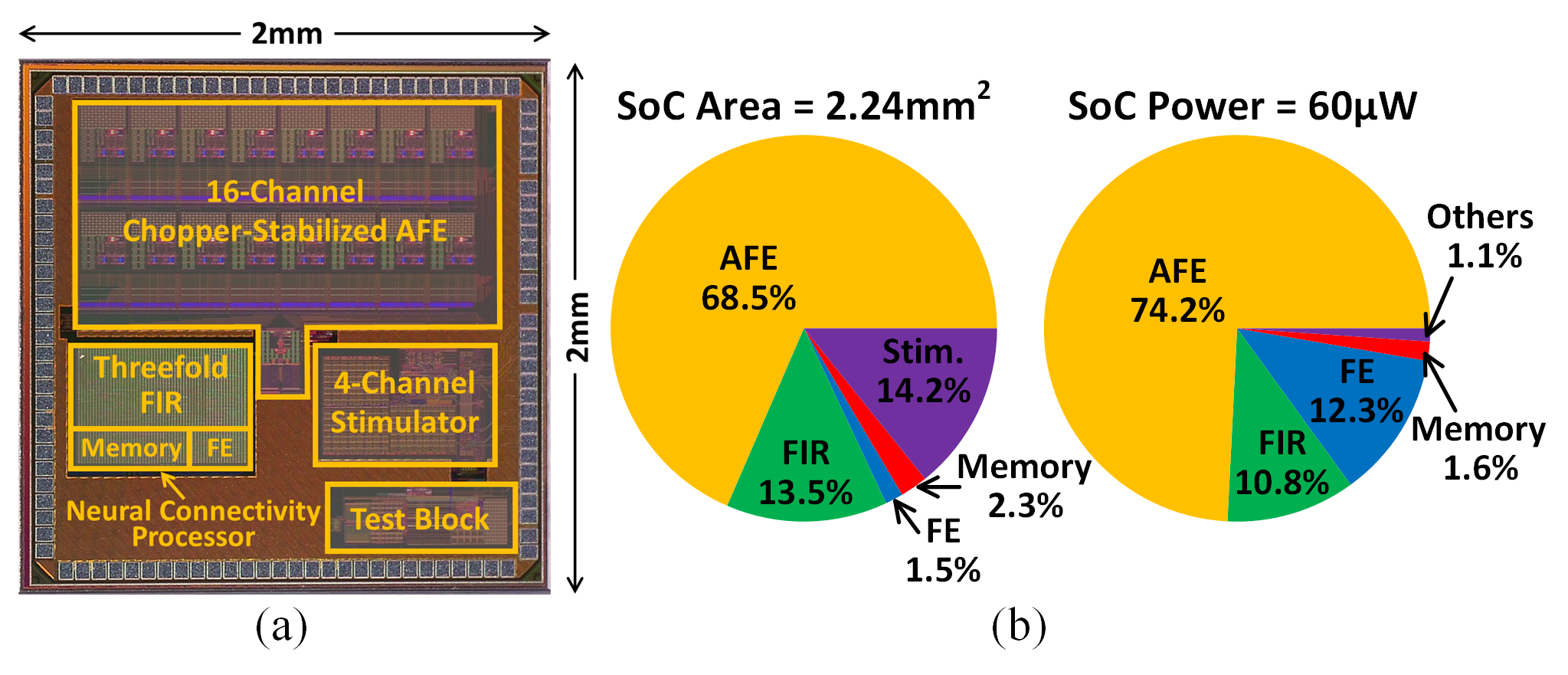

Silicon Implementation and Power Analysis

The SoC is fabricated in 65nm CMOS, occupying 2.24mm2 and consuming 60$\upmu$W at 1.2V/0.85V analog/digital supplies. Area and power breakdowns indicate efficient resource utilization across AFE, FIR, LPE, feature extractor, and stimulator subsystems.

Figure 7: (a) Chip micrograph, and (b) SoC area and power breakdowns.

Experimental Results

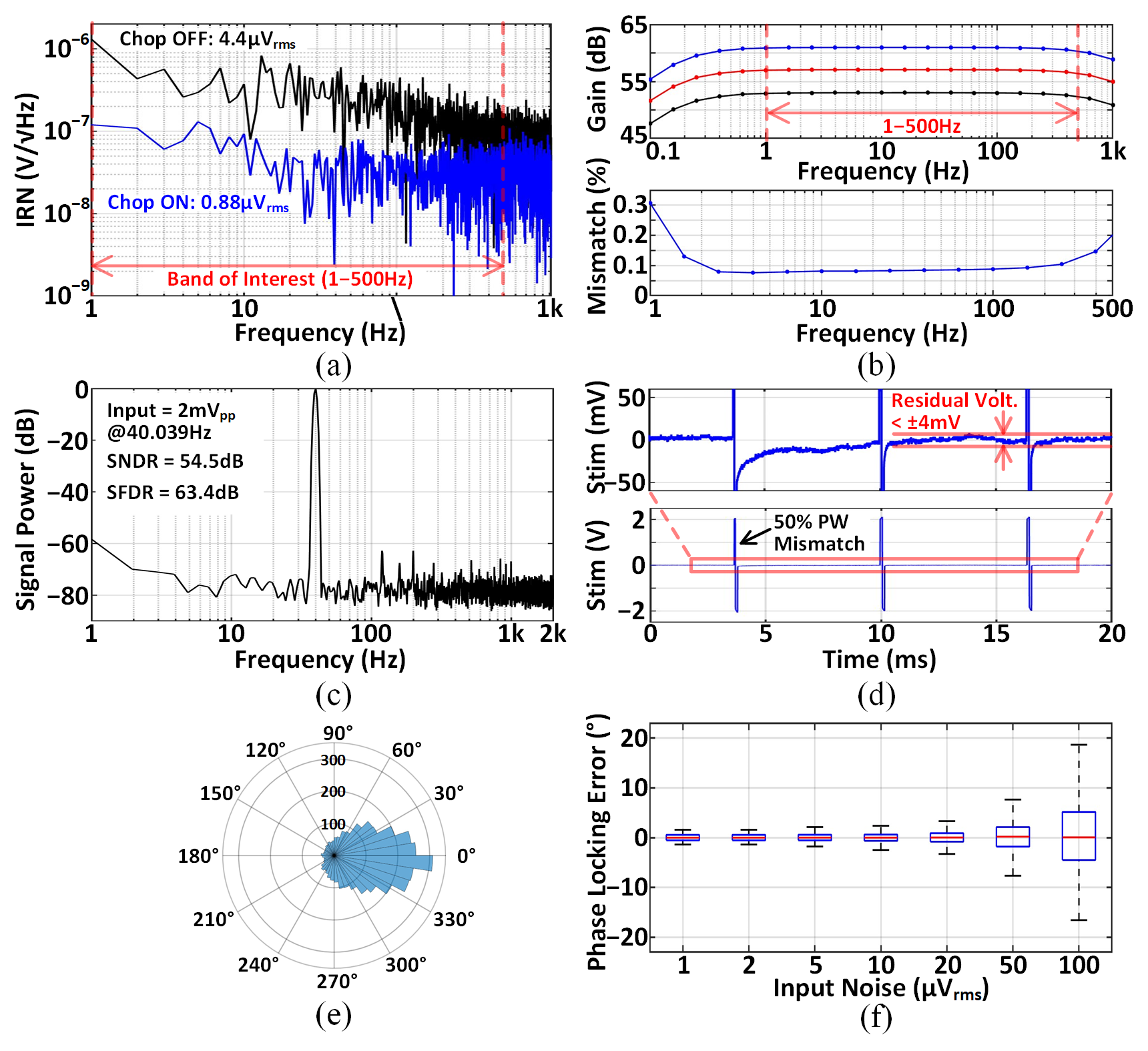

Benchtop Validation

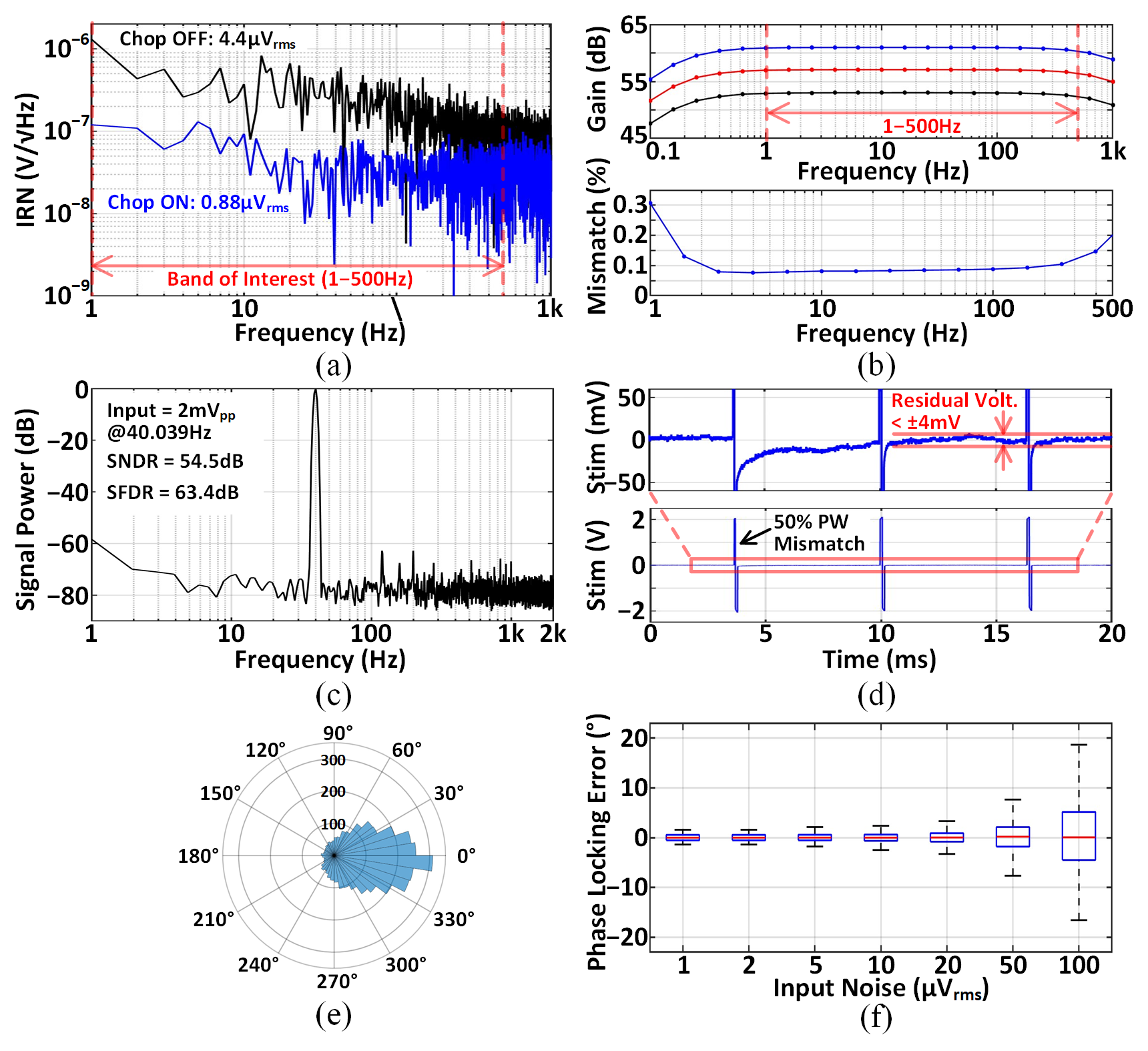

Input-referred noise (IRN) is reduced from 4.4$\upmu$Vrms to 0.88$\upmu$Vrms via chopper stabilization. Gain programmability (53–61dB) and matching (σ/mean<0.1%) are demonstrated. SNDR and SFDR are measured at 54.5dB and 63.4dB, respectively. Charge balancing reduces residual voltage to <4mV under intentional pulse width mismatch. Phase locking errors are tightly grouped around 0∘ when stimulation is triggered at 180∘ of theta-band oscillations, with FIR group delay compensated in the trigger timing. Noise tolerance analysis shows that phase locking accuracy is robust to increased input noise, suggesting potential for further power savings in the AFE.

Figure 8: Benchtop measurement results: AFE IRN, gain matching, dynamic performance, stimulator charge balancing, phase locking errors, and noise tolerance.

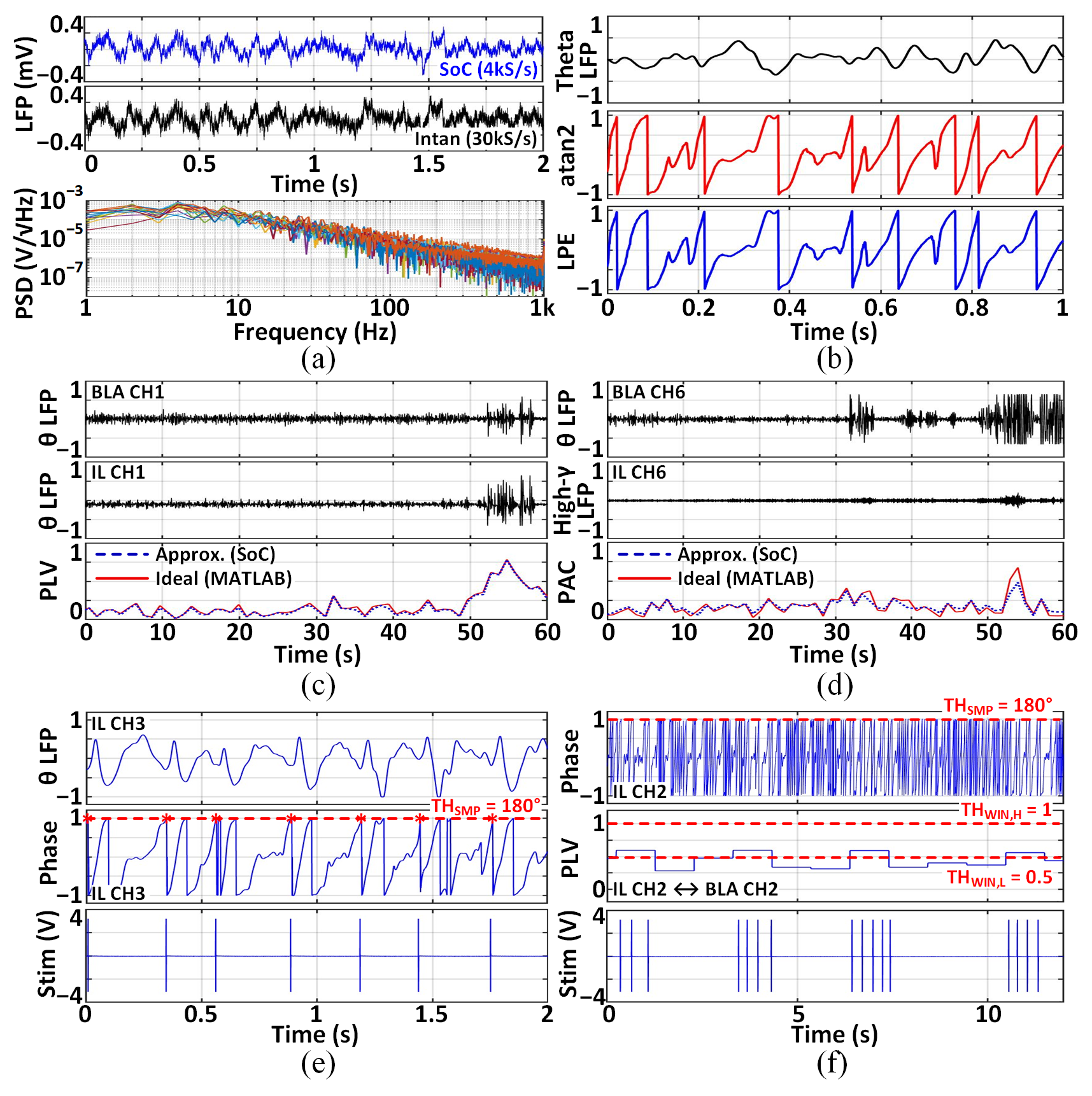

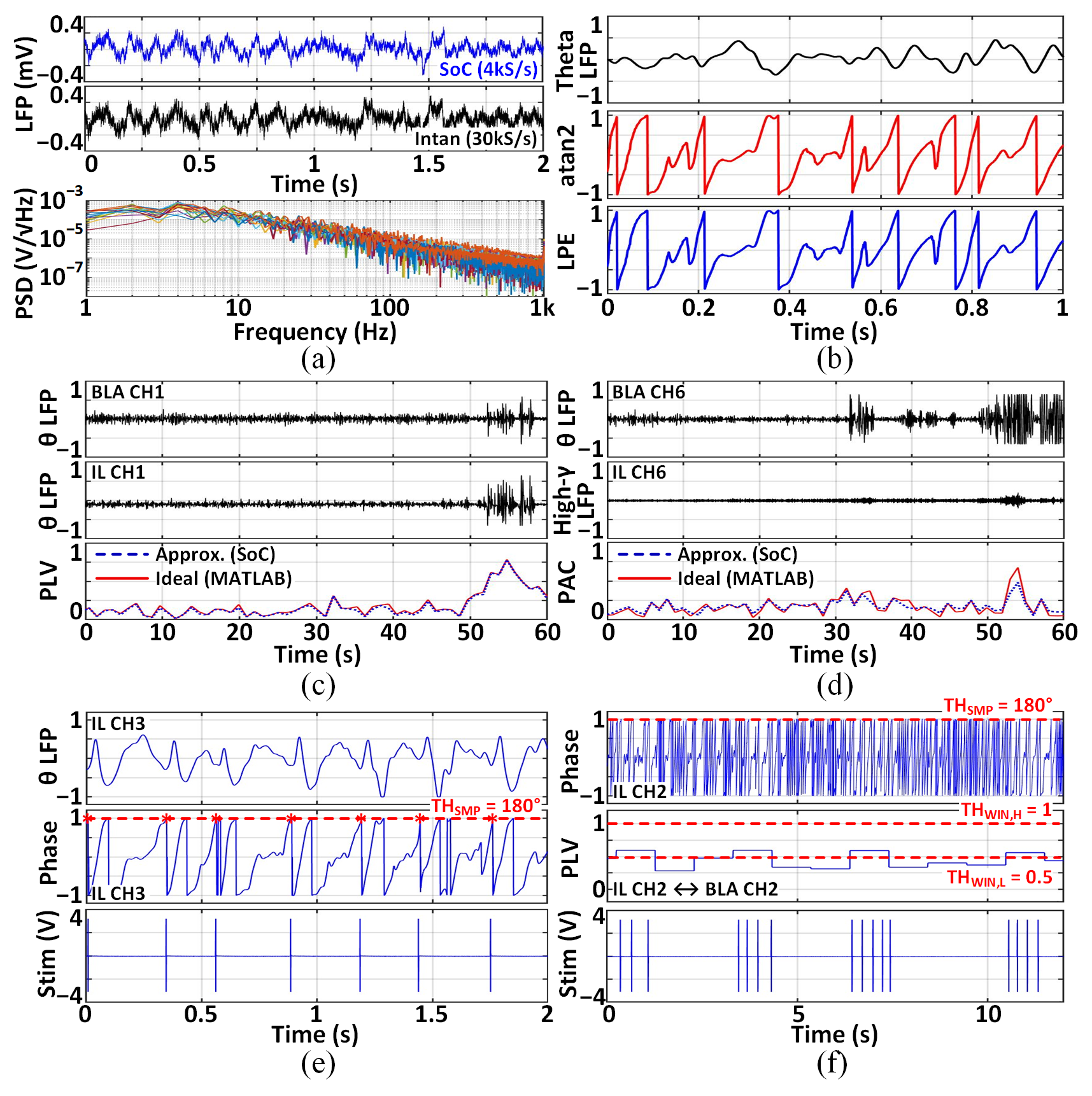

In-vivo Validation

Implantation in Long-Evans rats targets the basolateral amygdala and infralimbic cortex, focusing on theta-band oscillations relevant to fear and anxiety. The SoC records LFPs with expected 1/f PSD, and LPE phase extraction matches MATLAB ground truth. Approximated PLV and PAC features closely track ideal values. Closed-loop stimulation is demonstrated, triggered by instantaneous phase and by combined PLV-phase criteria, with maximum stimulation frequency set to 6Hz.

Figure 9: In-vivo measurement results: LFP recordings, phase extraction, PLV/PAC features, phase-locked and PLV-locked stimulation.

Comparative Analysis

Compared to state-of-the-art neural connectivity processors, this SoC achieves a superior energy-accuracy trade-off for instantaneous phase and connectivity extraction, with >60% power savings and flexible multi-mode stimulation control. It is the first to demonstrate phase-locked DBS in a compact, low-power SoC.

Implications and Future Directions

The presented SoC enables real-time, multi-channel neural connectivity analysis and phase-locked stimulation in a highly energy-efficient manner, supporting advanced closed-loop neuromodulation paradigms. The hardware-efficient LPE and feature extractor architectures are directly applicable to next-generation implantable devices for movement, psychiatric, and memory disorders. The demonstrated robustness to input noise and flexible biomarker integration suggest further opportunities for power optimization and expanded biomarker sets. Future work may explore scaling to higher channel counts, integration with adaptive machine learning classifiers, and translation to human clinical studies.

Conclusion

This work introduces a 16-channel low-power SoC for neural connectivity extraction and phase-locked DBS, validated through benchtop and in-vivo experiments. The system achieves precise, energy-efficient phase and connectivity measurement, robust charge-balanced stimulation, and flexible multi-mode control, representing a significant advance in closed-loop neuromodulation hardware. The architecture and algorithms presented have direct implications for the development of next-generation implantable devices for network-based brain disorders.