- The paper introduces ReSiPI, a chiplet network architecture that uses PCMs and dynamic gateway management to achieve improved power efficiency and reduced latency.

- It leverages adaptive bandwidth allocation through reconfigurable silicon-photonic interposers to address congestion in 2.5D chiplet systems.

- Performance benchmarks show over 53% energy consumption improvement and competitive latency metrics compared to prior models.

ReSiPI: A Reconfigurable Silicon-Photonic 2.5D Chiplet Network with PCMs for Energy-Efficient Interposer Communication

The paper introduces ReSiPI, a novel reconfigurable silicon-photonic 2.5D chiplet network architecture. It leverages phase-change materials (PCMs) to enhance energy efficiency for interposer communication while significantly addressing network congestion and power consumption challenges in chiplet systems. ReSiPI dynamically manages bandwidth allocation through adaptive gateway mechanisms, offering improved latency, power, and energy metrics compared to previous designs.

Introduction to 2.5D Chiplet Systems

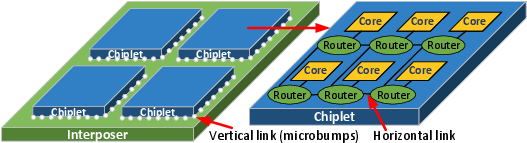

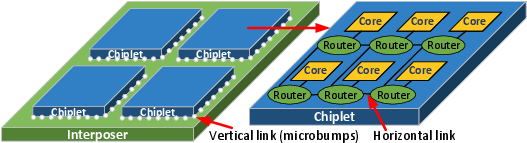

The advent of data- and compute-intensive applications has necessitated the development of large-scale chips that incorporate a vast number of processing cores. However, manufacturing yield issues associated with large chips have given rise to 2.5D chiplet systems. By disintegrating a large monolithic chip into smaller chiplets connected via an inter-chiplet interposer, these systems enhance manufacturing yield and scalability.

Figure 1: An example of a 2.5D chiplet system with four chiplets connected through an interposer.

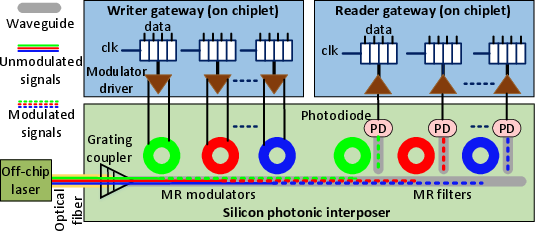

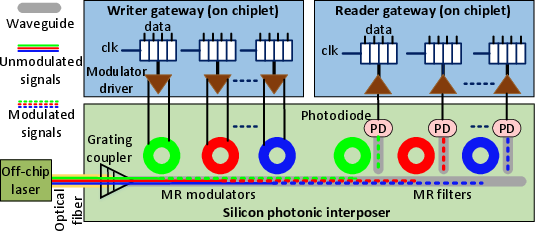

Conventional electronic interposers often face challenges of high latency and bandwidth limitations. Connecting chiplets using a photonic interposer network offers a promising alternative, providing low latency and handling higher data volumes efficiently. However, silicon-photonic interposers come with significant power consumption pressures, particularly due to the high laser power required for managing numerous optical wavelengths.

Silicon Photonic Interposers and PCM Integration

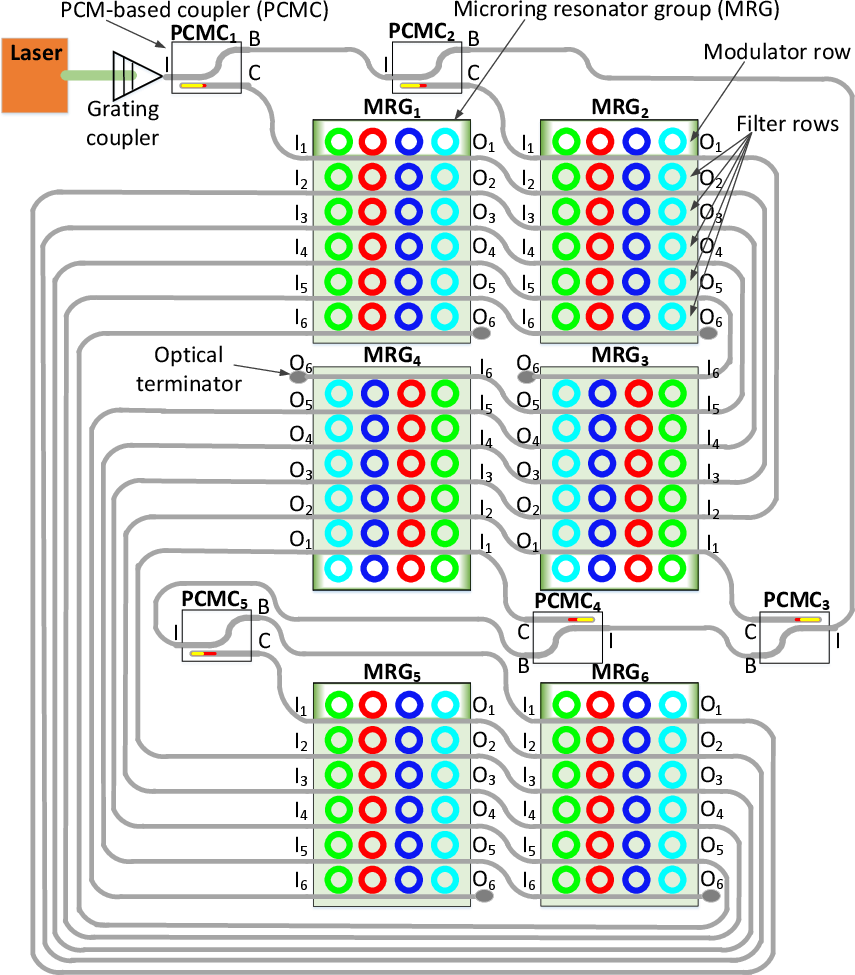

ReSiPI introduces a novel approach, where bandwidth is dynamically managed by adjusting the number of active gateways rather than the number of wavelengths, offering a fine-tuned power-performance balance.

Figure 2: Data transmission on a photonic interposer.

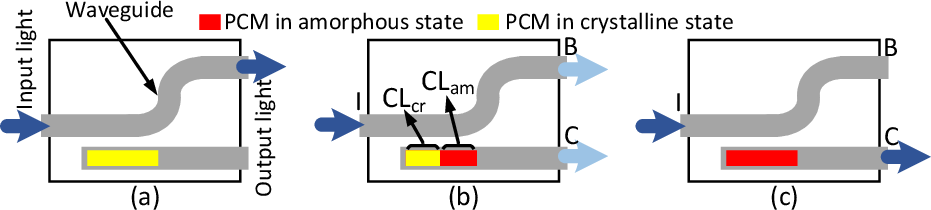

To optimize power usage, ReSiPI employs PCM-based couplers that effectively manage optical signal pathways, drastically reducing power consumption by enabling non-volatile reconfiguration. The PCM couplers change states to manipulate signal paths without continuous energy input, which significantly enhances network power efficiency.

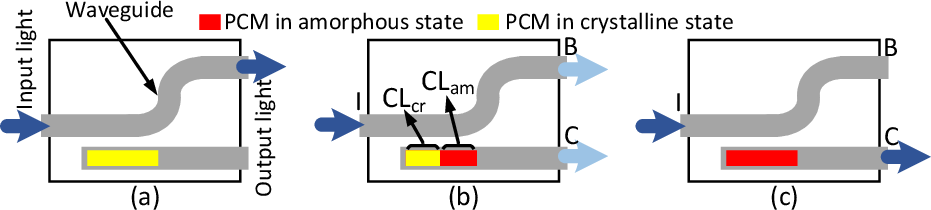

Figure 3: A PCM-based coupler (PCMC) in different states: (a) crystalline state to guide light to Bar (B) output, (b) partially crystalline state to guide a portion of light to the Cross (C) output and the rest to the Bar output, and (c) amorphous state to guide the input light to the Cross output.

ReSiPI Architecture and Dynamic Management

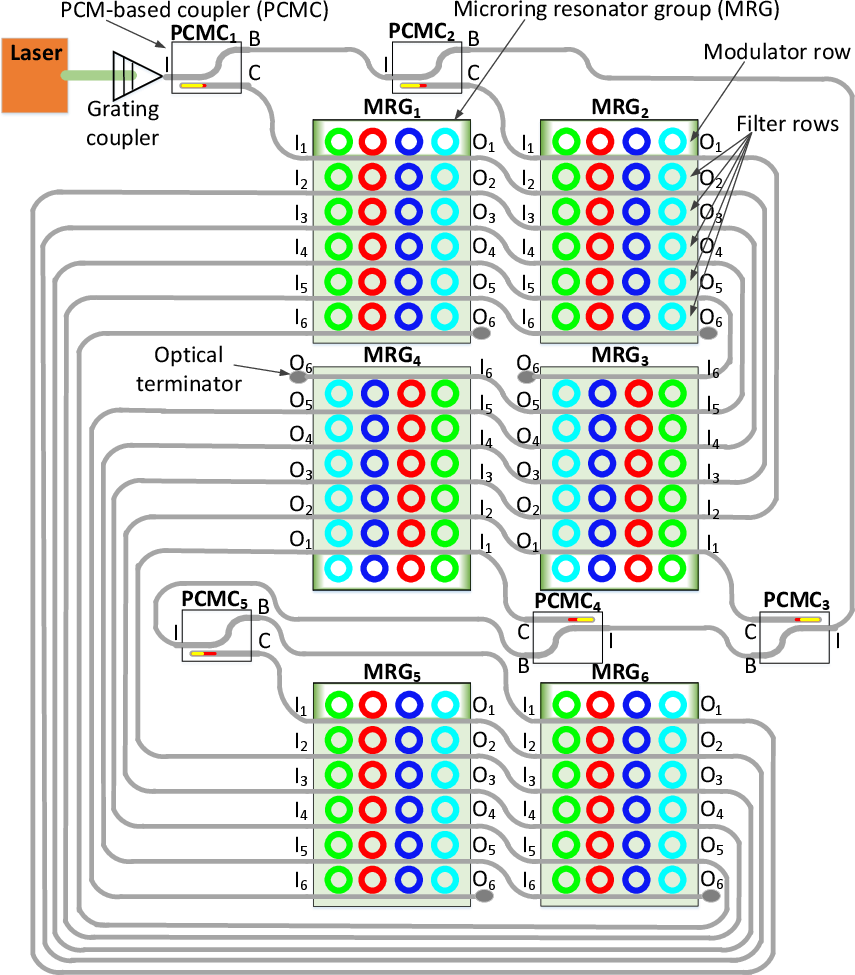

ReSiPI's architecture incorporates multiple gateways per chiplet and specializes in dynamically activating or deactivating these gateways based on monitored traffic loads. This design facilitates bandwidth distribution across gateways, effectively addressing congestion while optimizing power expenditure.

Figure 4: An example of the proposed photonic interposer architecture (ReSiPI) with a total of six gateways (one per chiplet) and four optical wavelengths.

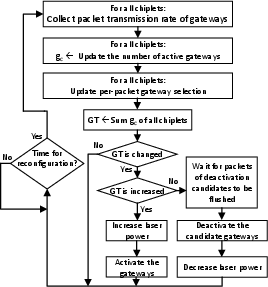

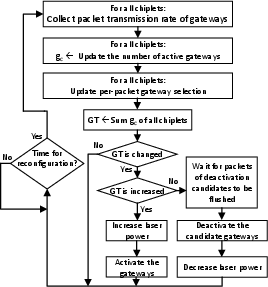

The adaptive gateway mechanism allows for real-time management of traffic distribution, wherein inactive gateways can be power-gated, reducing unnecessary power consumption. The control of gateway utilization dynamically adapts to changing traffic conditions to maintain efficient operation across varied workloads.

Figure 5: Dynamic gateway management in ReSiPI.

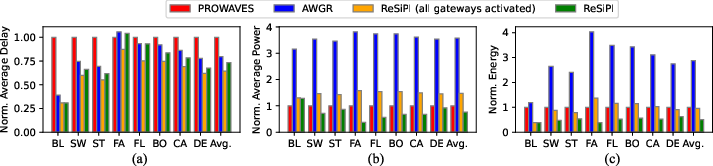

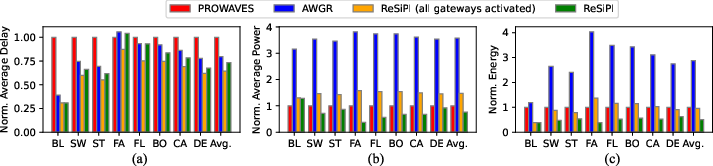

ReSiPI outperforms previous models such as the AWGR and PROWAVES in several benchmark applications, offering significant reductions in latency and power usage across a variety of scenarios. With its intelligent adaptation mechanisms, ReSiPI efficiently optimizes gateway activation, yielding substantial energy savings and improved network responsiveness.

Figure 6: (a) Normalized average latency, (b) Normalized average power, and (c) Normalized energy.

The adaptability of ReSiPI is demonstrated through dynamic performance metrics, where it rapidly adjusts to changes in traffic conditions, showcasing over 53% improvement in energy consumption while maintaining competitive latency figures.

Conclusion

ReSiPI establishes itself as a robust solution for next-generation chiplet systems, addressing key challenges in power efficiency and traffic management. Its innovative use of PCM technology and dynamic gateway strategies enables significant enhancements in network performance and energy optimization, marking a pivotal advance in photonic interposer architectures.

Overall, ReSiPI's approach constitutes a viable pathway for the future development of scalable, energy-aware chiplet systems and underscores the critical role of intelligent reconfiguration in high-performance network architectures.