- The paper demonstrates a novel method using constraint-aware e-graphs to automate RTL datapath optimization.

- It applies sub-domain equivalences and ASSUME-driven rewrites, achieving a 41% area reduction and 33% delay improvement in floating-point subtractors.

- Additional case studies on float-to-unorm conversion and video interpolation confirm the approach’s adaptability and efficiency across various designs.

Automating Constraint-Aware Datapath Optimization using E-Graphs

Introduction

The paper explores the application of constraint-aware optimization techniques in register-transfer level (RTL) design via e-graphs, aiming to surpass existing electronic design automation (EDA) tools. This study demonstrates how e-graphs, augmented with enforced constraint awareness, effectively improve the optimality and efficiency in the design of hardware components, specifically focusing on floating-point subtractors. The approach leverages the styrofoam-egg library to facilitate aggressive optimization in datapath circuits by exploiting conditional branch constraints.

Background

At the heart of the proposed method is the use of e-graphs, which efficiently represent equivalence classes of expressions and facilitate syntactic rewrites by applying equivalences. E-graphs have seen success in various domains by compactly representing multiple semantically equivalent implementations of an expression. By incorporating constraint-aware optimization into e-graphs, the method extends their utility, allowing specified branches in a hardware design to be further optimized for performance and area efficiency.

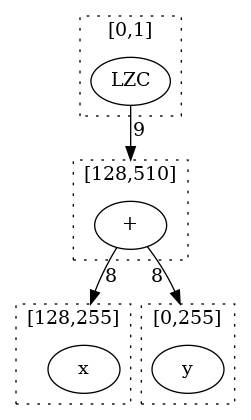

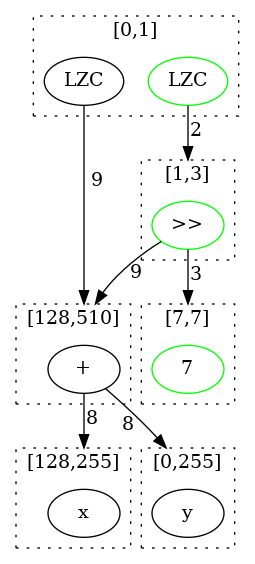

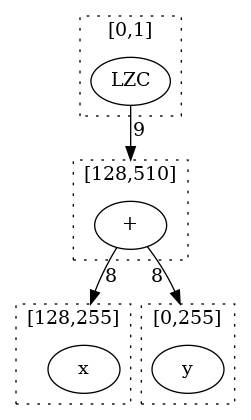

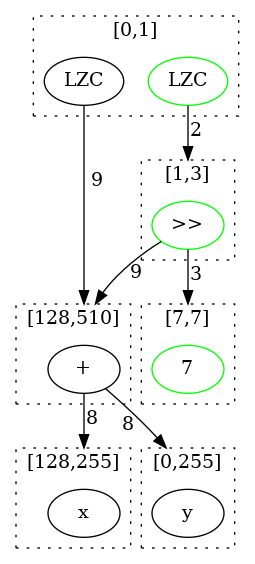

Figure 1: Initial e-graph represents LZC operations showcasing structural transformations before the rewrite.

Theory and Implementation

Sub-Domain Equivalences

The technique of sub-domain equivalence allows expressions within circuits to be optimized under specific constraints. By leveraging abstract interpretation, particularly interval arithmetic, this theory captures potential optimization opportunities exposed by conditional branches. Each expression is associated with input value ranges, enabling constraint-based sub-domain congruences. This rigorously refining tactic allows the rewriting of entire e-graphs under branch-specific assumptions, improving both the representation and efficiency of programs.

E-Graph Construction and Rewriting

E-graphs utilize custom-developed rewrites tailored to introduce and propagate assumptions via the ASSUME node, simplifying the expression transformation under branch-specific constraints. Alongside condition rewriting, this procedural methodology enables deep optimization by considering potential values and applying modular arithmetic conservatively. The egg library facilitates the symbolic manipulation, with additional rewrites developed to exploit hardware-specific intricacies such as bitwidth propagation and casting operations.

Case Study: Floating-Point Subtraction

The proposed optimization process was exemplified by automatically optimizing a hardware implementation of a floating-point subtractor. Traditionally, floating-point hardware design demands handcrafted optimization, often leading to complex logic circuits. By utilizing branching logic that dictates different computational paths based on input constraints, the approach was able to significantly condense the subtractor's design.

The optimized architecture notably reduced the subtraction bit-length requirements and implemented a bifurcating path design (near-path/far-path method), efficiently managing potential catastrophic cancellations in floating-point computation. As a result, this yielded a design that was 41% smaller in area and had reduced delay by 33% compared to initial implementations.

Additional Test Cases

Further experiments on diverse designs like float to unorm conversion and video interpolation exemplified the method's adaptability and effectiveness. Each test case demonstrated significant reductions in area and negligible increases in delay, underpinning the technique's viability across various IEEE-compliant RTL designs.

Conclusion

The exploitation of e-graphs for constraint-aware datapath optimization provides a robust framework to achieve highly efficient RTL designs, matching or exceeding human-crafted solutions. The ease of adopting these methodologies into existing EDA workflows offers substantial benefits, potentially driving innovation in automatic architectural discovery. Future research may involve extending models to include more granular delay attributes or integrating optimization criteria like energy consumption for multifunctional design space exploration.