- The paper presents an integrated, photonics-aware planning framework that automates electrical routing for large-scale active PICs.

- It employs a crossing-aware A* search and novel track assignment to reduce via usage by up to 99% and design rule violations by 98%.

- The framework achieves a 17-fold reduction in runtime, significantly enhancing scalability and efficiency in EPIC design automation.

Photonics-Aware Planning-Guided Automated Electrical Routing for Large-Scale Active Photonic Integrated Circuits

The paper presents a comprehensive solution to the challenge of electrical routing in large-scale Active Photonic Integrated Circuits (PICs). This solution integrates waveguides with metal interconnects in a unified, automated design flow, specifically addressing the deficiencies of conventional VLSI routing tools when applied to PICs.

Introduction to Active PIC Routing Challenges

Active PICs, poised to revolutionize photonic computing with their applications in AI hardware and optical interconnects, present unique routing challenges. These challenges stem primarily from their dense arrays of photonic and electronic components which require meticulous routing of both waveguides and electrical interconnects. Traditional manual routing approaches are increasingly impractical due to the scale and complexity involved.

Figure 1: Electrical and optical routing in active PICs, showing the complexity faced in manual approaches.

Given these challenges, the paper proposes an end-to-end automated routing framework designed to handle the inherently different constraints of photonic devices, such as avoiding prolonged wire overlap with optical paths to reduce thermal and insertion loss.

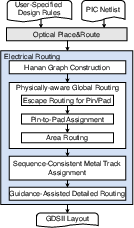

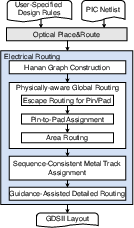

Overview of the Proposed Framework

The framework adopts a physically-aware global planning approach that jointly tackles waveguides and electrical routing. The global planner generates routes that minimize congestion and crossings while adhering to the physical constraints presented by photonic components. The proposed solution consists of several key components:

- Global Electrical Routing Planner: This module generates initial routing guides that are photonic-aware, minimizing crossing and via usage.

- Track Assignment with Sequence Consistency: Ensures high routability by respecting established net orders and avoiding crossing-over congestion points.

- Soft Guidance-Assisted Detailed Routing: This technique helps maintain route quality and close adherence to global routing guides even in the presence of localized layout blockages.

Figure 2: Algorithm flow of the proposed active PIC electrical routing framework, depicting an integrated approach to waveguide and metal wire routing.

Implementation Details

Hanan Grid Construction

The routing process begins with the construction of a customized Hanan grid over the layout. This grid considers photonic components as soft blockages and facilitates congestion-aware multi-layer planning.

Global Routing with Crossing-Aware A*

In the global stage, a crossing-aware A* search with net-sequence constraints is employed to ensure that generated pathways avoid topological crossings. This stage is critical for minimizing layer usage and reducing risk of later routing failures.

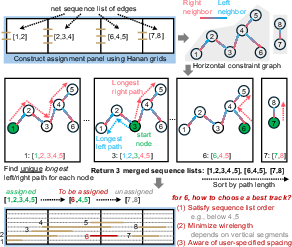

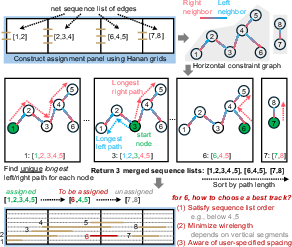

Track Assignment Algorithm

After global routing, the framework applies a novel track assignment method that respects the sequence of the paths. By utilizing an assignment panel and constraint graphs, the framework dynamically allocates tracks to routes, thus enhancing scalability and effectiveness.

Figure 3: Track assignment procedure ensures logical routing order and adheres to photonic interaction constraints.

Detailed Routing with Soft Guidance

The detailed routing phase implements a soft guidance mechanism that provides more flexibility than a hard-guideline enforcement approach. By allowing temporary deviations, it accelerates the routing process while minimizing design rule violations.

Evaluation and Results

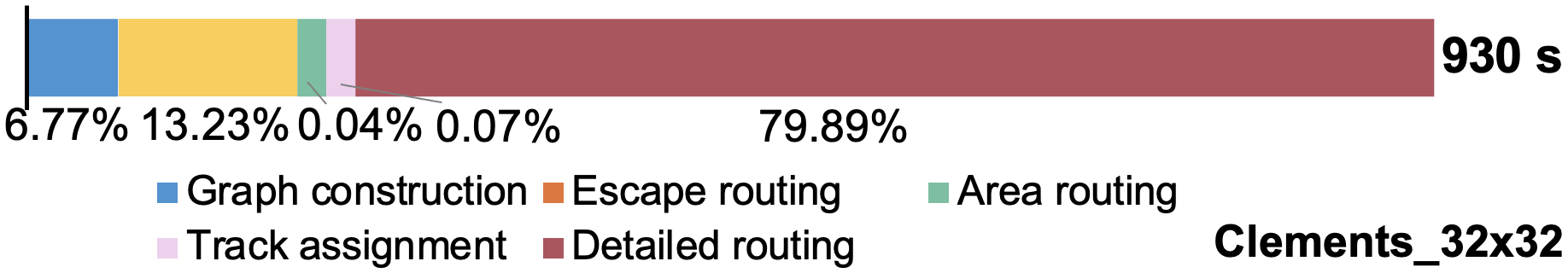

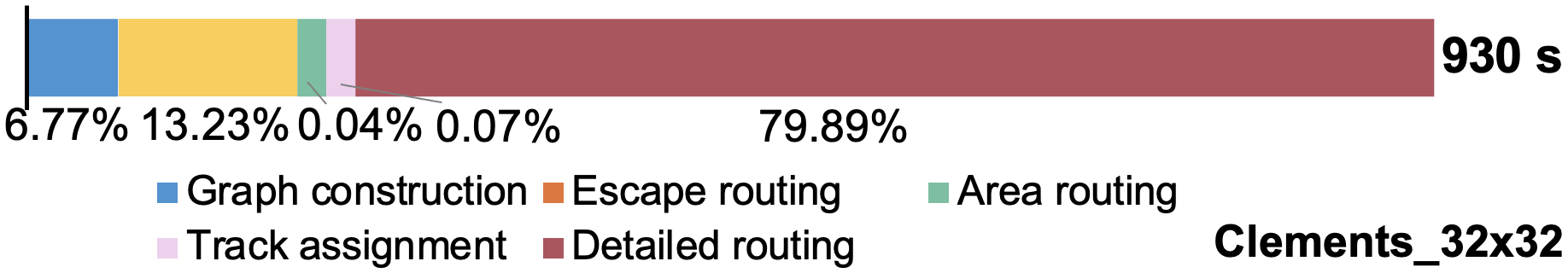

The framework was evaluated on a suite of benchmarks representing various large-scale PIC designs. The evaluation demonstrated a significant reduction in via usage (up to 99%) and design rule violations (up to 98%) compared to traditional approaches, whilst achieving a 17-fold reduction in runtime.

Figure 4: Runtime breakdown demonstrating the efficiency gains achieved by the proposed routing framework.

Conclusion

This work introduces a pioneering routing framework for active PICs, addressing the intricate requirements and interactions between photonic and electrical components. It fills a critical gap in photonic-electronic design automation, paving the way for scalable and efficient EPIC design. As the integration of photonic circuits into commercial applications progresses, such automated approaches will be essential to meet the demands for speed and reliability in EPIC implementations. Future work may focus on further optimizing routing algorithms and expanding the applicability to additional types of PICs and design rules.