Cyclic Hypergraph Product Code

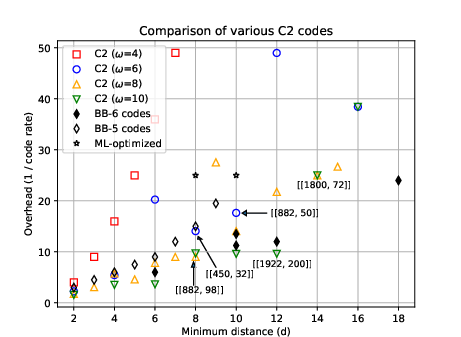

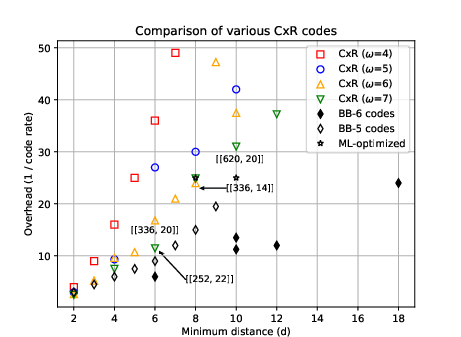

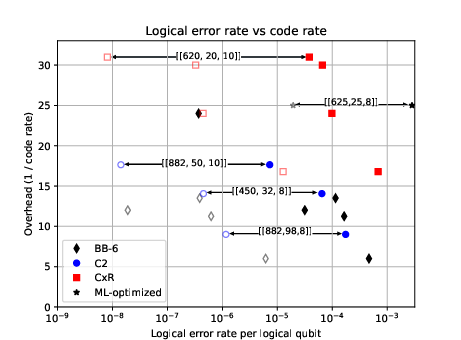

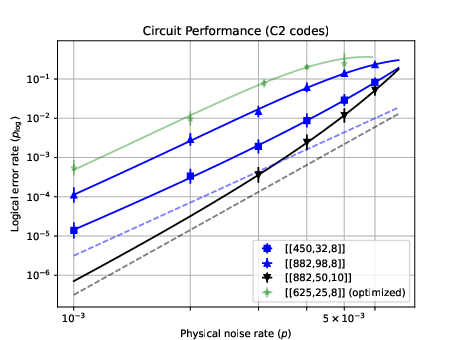

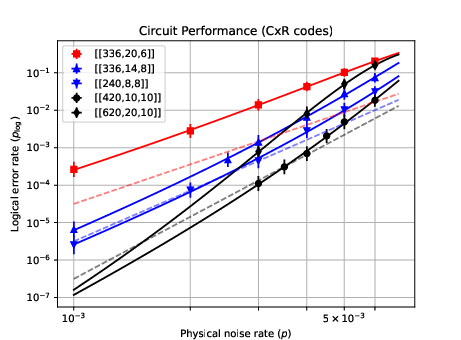

Abstract: Hypergraph product (HGP) codes are one of the most popular family of quantum low-density parity-check (LDPC) codes. Circuit-level simulations show that they can achieve the same logical error rate as surface codes with a reduced qubit overhead. They have been extensively optimized by importing classical techniques such as the progressive edge growth, or through random search, simulated annealing or reinforcement learning techniques. In this work, instead of ML algorithms that improve the code performance through local transformations, we impose additional global symmetries, that are hard to discover through ML, and we perform an exhaustive search. Precisely, we focus on the hypergraph product of two cyclic codes, which we call CxC codes and we study C2 codes which are the product a cyclic code with itself and CxR codes which are the product of a cyclic codes with a repetition code. We discover C2 codes and CxR codes that significantly outperform previously optimized HGP codes, achieving better parameters and a logical error rate per logical qubit that is up to three orders of magnitude better. Moreover, some C2 codes achieve simultaneously a lower logical error rate and a smaller qubit overhead than state-of-the-art LDPC codes such as the bivariate bicycle codes, at the price of a larger block length. Finally, leveraging the cyclic symmetry imposed on the codes, we design an efficient planar layout for the QCCD architecture, allowing for a trapped ion implementation of the syndrome extraction circuit in constant depth.

Paper Prompts

Sign up for free to create and run prompts on this paper using GPT-5.

Top Community Prompts

Explain it Like I'm 14

Overview

This paper is about making quantum computers more reliable. Quantum machines are very sensitive to tiny errors, so they need “error-correcting codes” to protect information. The authors introduce a simple, highly structured way to build one of the best-known families of quantum error-correcting codes, called hypergraph product (HGP) codes. Their version uses repeating, circular patterns (cyclic structures), and they show that these “cyclic HGP codes” can beat previously optimized codes in simulations, and can be laid out efficiently on real hardware.

What questions did the researchers ask?

The authors focused on three main questions:

- Can adding global symmetry (regular repeating patterns) to HGP codes make them perform better than codes found by random or machine-learning searches?

- Which specific cyclic HGP designs are best: combining a cyclic code with itself (C2), or combining a cyclic code with a simple repetition code (CxR)?

- Can these codes be implemented easily on realistic hardware with fast error checks (constant-time syndrome extraction)?

How did they do it? (Methods made simple)

To explain their approach, let’s break down some ideas using everyday language.

What is a quantum error-correcting code?

Think of storing a message by spreading it across many puzzle pieces (qubits). If some pieces get smudged (errors), you can still recover the message by checking certain patterns (“checks”) that should always match. These checks don’t look directly at the secret message—so they don’t destroy it—they only look for inconsistencies.

“LDPC” (low-density parity-check) codes are special because each check only touches a few pieces, making them practical to run over and over.

What are hypergraph product (HGP) codes?

An HGP code is built by combining two simpler “classical” codes into a bigger, stronger quantum code. Imagine taking two small Lego patterns and snapping them together to build a sturdy wall. HGP codes are attractive because they can protect many logical qubits (the useful information) while keeping checks small.

What does “cyclic” mean here?

“Cyclic” means the pattern repeats in a loop—like beads on a bracelet. Using cyclic structures creates strong symmetry: checks and qubits are arranged so many parts look the same, just shifted. This symmetry reduces the number of possibilities the researchers need to search through and often produces cleaner, more balanced codes.

The paper studies two simple subfamilies:

- C2: product of a cyclic code with itself (a symmetric design).

- CxR: product of a cyclic code with a basic repetition code (very simple and hardware-friendly).

Finding good codes (exhaustive search)

Previous works often used random choices or machine learning to tweak codes. Instead, the authors impose symmetry (cyclic patterns) and then perform an exhaustive search within that smaller, structured space. They look at many cyclic building blocks (of modest size) and combine them to make HGP codes, keeping only those with promising properties (good “distance,” good rate, and low-weight checks).

Key idea: Global symmetry is hard for local, ML-based tweaking to discover, but it can unlock much better performance.

Testing with realistic simulations

They run circuit-level simulations, which model the full process of measuring checks using gates that can fail with some small probability (for example, 0.1% failure). This is more realistic than simplified models and gives a better sense of how the code would behave on actual hardware.

They measure:

- Logical error rate: the chance that the protected information flips or gets corrupted.

- Overhead: how many physical qubits you need per logical qubit (lower is better).

- Minimum distance (d): how many physical errors the code can tolerate before it fails (higher is better).

When you see something like [[882, 50, 10]], it means:

- 882 physical qubits total,

- 50 logical qubits stored,

- minimum distance 10.

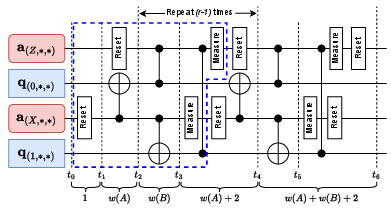

Designing the hardware layout

They propose a simple layout: two rows of qubits (a 2 × n array):

- Top row: data qubits (hold the message).

- Bottom row: ancilla qubits (used to check for errors).

Because the code is cyclic, they can “shift” the bottom row like a conveyor belt to line up with the top row exactly when needed. This lets them run the entire check circuit in constant depth—meaning the time to perform a full round of checks doesn’t grow as the code gets bigger. That’s excellent for practical devices like trapped ions or other platforms that can move qubits.

What did they find and why it matters?

Here are the main results, introduced in a sentence and then listed:

The authors discovered cyclic HGP codes that significantly outperform previous best-known HGP codes and rival a leading family called bivariate bicycle (BB) codes.

- Strong performance vs ML-optimized HGP: A C2 code [[882, 50, 10]] achieves a logical error rate per logical qubit below 2×10⁻⁸ at a typical noise level, while a previous ML-optimized code [[625, 25, 8]] achieves about 2×10⁻⁵—roughly 1,000 times worse.

- Good trade-offs: Another C2 code [[450, 32, 8]] matches the minimum distance of prior ML-optimized HGP codes but with fewer qubits and more logical qubits, and reaches a logical error rate per logical qubit of about 4.5×10⁻⁷.

- Simple CxR codes perform well too: Even the very simple CxR designs beat ML-optimized HGP codes in logical error rate, despite their simplicity.

- Competitive with BB codes: Some C2 codes achieved similar or even better logical error rate per logical qubit and lower qubit overhead than BB codes, although HGP codes generally have larger total block length (more total qubits).

- Efficient hardware layout: Thanks to cyclic symmetry, they designed a constant-depth syndrome extraction circuit in a compact 2-row layout compatible with real platforms like trapped ions using a QCCD-style architecture. Constant depth means checks run fast regardless of code size.

Why it matters: Lower logical error rates mean more reliable quantum computations. Lower overhead means fewer qubits needed per useful qubit, which is crucial because qubits are scarce and expensive. A simple, constant-depth layout makes it easier to build and scale the hardware.

Implications and potential impact

This work shows that adding global symmetry (cyclic patterns) to HGP codes can unlock big gains that local optimization methods tend to miss. Practically, it offers:

- Better reliability for quantum memory and computation, potentially beating popular baselines (like surface codes and ML-optimized HGP) in important regimes.

- A hardware-friendly, constant-depth check circuit that fits well with ion-trap and other movable-qubit systems.

- A clear, systematic way to find strong codes without relying on random tuning or complex machine learning.

Looking ahead, these cyclic HGP codes could become key building blocks for fault-tolerant quantum computers. The authors focus on memory and error correction here; designing fast, reliable logical gates on top of these codes is an important next step, and existing techniques may transfer well to this structured setting.

Knowledge Gaps

Knowledge gaps, limitations, and open questions

Below is a concise list of unresolved issues, limitations, and concrete research directions raised by the paper.

- Precise asymptotic guarantees for cyclic HGP families: The paper demonstrates strong finite-size performance but does not establish rigorous rate–distance scaling for CxC/C2/CxR codes (e.g., whether these cyclic restrictions preserve polynomial distance, what exponent is achieved, and how rate scales asymptotically as check weight and cyclic length grow).

- Minimum-distance characterization under cyclic constraints: The claim that the CxC code’s distance is the minimum of the underlying classical distances is inherited from general HGP results, but a rigorous treatment for cyclic seed families (including dependencies introduced by cyclic symmetry and transpose equivalences) is not provided. A constructive distance proof or efficient exact distance computation for representative instances is missing.

- Decoder dependence and optimality: Simulations use BP+OSD (10,000 BP iterations, 5th-order OSD). It is unclear whether the performance advantage persists across modern decoders (e.g., union-find variants, MWPM adaptations for LDPC, tailored message-passing exploiting cyclic symmetry, neural decoders), or whether cyclic symmetry enables specialized fast/FFT-based BP with better accuracy/latency.

- Threshold estimation and finite-size scaling: No threshold estimates are provided for C2/CxR codes. Systematic scaling studies (distance or size ladders) to extract pseudothresholds/thresholds under circuit noise are absent, limiting comparisons to surface/BB codes beyond specific instances.

- Noise model realism: The “standard circuit noise” model (independent depolarizing channels after gates/measure/reset/idle) excludes platform-specific error modes (e.g., transport-induced dephasing, motional heating, SPAM asymmetry, coherent/correlated errors, leakage, drift, crosstalk, biased Pauli channels). Robustness of CxC/C2/CxR codes and their layout under realistic errors remains unquantified.

- Transport-induced errors in cyclic layout: The proposed QCCD-aligned two-row cyclic shift layout assumes constant-depth extraction dominated by a count of monomials. The impact of ion shuttling distances, speed limits, cooling steps, additional idle windows, and transport error accumulation on logical performance and depth/latency is unaddressed.

- Hook-error robustness: The paper suggests an advantage of HGP codes vs hook errors but does not quantify hook-error mechanisms under the proposed extraction schedule (e.g., gate sequencing and ancilla reuse), nor compare to BB/surface layouts with hook-mitigation. Formal analysis or targeted simulations are needed.

- Planar layout depth vs device timing: The depth formula in Proposition 4 counts logical gate layers and cyclic shifts but ignores physical timing differences between gate execution and transport. Whether constant depth per round holds once transport durations, calibration/cooling pauses, and parallelism limits are accounted for requires hardware-aware scheduling analysis.

- Ancilla operations, resets, and reuse: The schedule interleaves CX/CZ and X-basis measurement/reset of ancillas. A detailed analysis of reset fidelity, measurement error, reset-induced crosstalk, and time-to-steady-state across rounds (including impact on BP decoding via temporal correlations) is missing.

- Syndrome compression and readout bandwidth: The cyclic structure may enable compressed readout patterns, but the paper does not explore syndrome compression, streaming decoding, or bandwidth constraints for large-block C2 codes in practical controllers.

- Decoder latency and resource usage: No runtime/memory profiling is provided for BP+OSD on the larger codes (e.g., [[882,50,10]]), nor an assessment of whether real-time decoding is feasible under QCCD cycle times and controller constraints.

- Reproducibility of code constructions: The exact generating polynomials and parameters of the best-performing cyclic seeds (e.g., explicit (x) and (y) monomials for the top C2/CxR instances) are not enumerated, making independent reproduction and comparative studies difficult.

- Search-space limitations: Exhaustive search is limited to classical cyclic codes with block length ≤ 40 and check weight ≤ 5 (implying HGP check weight ≤ 10). It is unknown whether relaxing these bounds (e.g., longer cyclic lengths, weights 6–8) yields further gains or introduces detrimental decoder artifacts (quantum trapping sets).

- Selection criteria alignment with quantum performance: Classical seed selection based on higher classical code rate may not correlate optimally with quantum circuit-level performance under BP+OSD. A principled quantum-aware selection metric (e.g., cycle structure, girth, absorption sets for BP, Tanner graph properties under CSS lift) is needed.

- Trapping sets and pseudo-codewords: The paper notes limited understanding of quantum trapping sets. A targeted study of absorbing/trapping structures in cyclic HGP Tanner graphs (and their relation to BP failure modes) is absent, despite the cyclic symmetry potentially creating predictable pseudo-codeword families.

- Impact of check-weight on circuit errors: While higher check weights improve parameters, circuit-level noise may worsen due to more two-qubit gates per check. A systematic trade-off study (check-weight vs logical error and depth/latency under realistic gate fidelities) is missing.

- Comparative analysis against BB codes beyond LER: The claim that some C2 codes beat BB-6 in logical error rate and overhead for certain regimes lacks a comprehensive resource comparison, including cycle time, depth per round, transport overhead, and decoder latency. A fair apples-to-apples hardware- and controller-aware comparison is needed.

- Generalization beyond repetition in CxR: The CxR family fixes one seed to a repetition code with b = d_c. Alternatives (e.g., short cyclic seeds with tailored spectra) that preserve layout simplicity but improve rate/distance are unexplored.

- Fault-tolerant logical gates: The paper defers logical gate design. Open questions include whether cyclic symmetry enables efficient transversal/LDPC-friendly logicals, scheduling for lattice surgery-style operations, and gate-induced noise amplification under the proposed layout.

- Multi-layer or modular architectures: While a two-row layout is proposed, extensions to multi-module ion chains or neutral atom arrays (with constrained interconnects) and their implications for scheduling, syndrome concurrency, and transport error aggregation are not analyzed.

- Robustness to bias and correlations: Performance under biased Pauli channels (e.g., dephasing-dominant platforms) and spatial/temporal correlations (e.g., common-mode shifts during transport) is not investigated; cyclic structure may allow tailored checks to exploit bias.

- Syndrome-round interleaving and memory errors: The interleaving of CX/CZ across rounds (Appendix) may induce temporal correlations and memory error accumulation. Quantifying their effect on decoding and scheduling optimizations is an open task.

- Hardware calibration and control complexity: The opposite-chirality cyclic shifts for X/Z ancilla streams may complicate control and calibration; the impact on error budgets and synchronization is not discussed.

- Tooling and datasets: Public release of code generators, instance lists, and Stim/BP+OSD scripts would enable broader benchmarking (including different noise models and decoders), but is not mentioned.

Practical Applications

Immediate Applications

The following applications can be pursued with current tools, simulators, and existing hardware that supports cyclic transport or equivalent reconfiguration. They leverage the paper’s explicit code families (C2 and CxR), circuit constructions, and layouts.

- Deployable logical memory on QCCD-like architectures (sectors: hardware, cloud QC)

- Use C2 and CxR codes as fault-tolerant quantum memory with constant-depth syndrome extraction on a 2×n layout with cyclic shifts.

- Target platforms: trapped ions (shuttling), neutral atoms (rearrangement), photonics (time-bin/flying qubits), spin qubits with conveyor/shift operations.

- Product/workflow: a “CxC logical memory” service tier for cloud providers offering improved logical error per logical qubit; parameterized offerings (e.g., [[450, 32, 8]] C2; [[882, 50, 10]] C2; CxR options for lower stabilizer weight).

- Assumptions/dependencies: reliable cyclic shift operations with opposite chirality for X/Z ancilla rows; fast measurement/reset; standard depolarizing-like noise near p≈10⁻³; decoder availability (BP+OSD); sufficient qubit counts for block lengths up to a few thousand.

- Hardware-aware control schedule synthesis for constant-depth QEC (sectors: hardware, software tooling)

- Implement Algorithm “CxC sparse cyclic layout” to automatically produce time-optimized, maximally packed syndrome-extraction circuits with round-interleaving.

- Tool/workflow: a compiler pass that generates gate schedules and transport patterns for the 2×n cyclic layout, minimizing depth via monomial grouping in the cyclic generators.

- Assumptions/dependencies: support for concurrent non-overlapping gates; calibrated transport timing; verified LDPC sparsity (check weights ≤10).

- Decoder configuration and integration (sectors: software, hardware operations)

- Integrate BP+OSD decoders tuned with the provided heuristic form for logical error rate (fit parameters available for benchmark instances).

- Workflow: standardized decoding pipelines using Stim circuits; heuristic-based runtime selection of code/decoder order based on current noise estimates (p).

- Assumptions/dependencies: decoder stability at large code sizes; availability of efficient OSD (order ≈5) and sufficient compute.

- Code selection and benchmarking toolchain for cyclic HGP families (sectors: academia, industry R&D)

- Adopt the paper’s exhaustive search strategy (cyclic classical seeds with length ≤40, weight 2–5) to rapidly generate candidate codes constrained by stabilizer weight and block length targets.

- Tool/product: a “CxC code catalog” with metadata (weight, block length, rank balance, minimum distance, rate), and circuit-level performance under standard noise.

- Assumptions/dependencies: reproducible simulation stack (Stim), comparable noise models across platforms, ongoing updates for hardware-specific error channels.

- Near-term performance benchmarking against BB codes and ML-optimized HGP (sectors: academia, cloud QC)

- Use the documented C2 instances that match or outperform BB-6 on logical error per qubit and overhead in certain regimes to guide platform choices.

- Workflow: side-by-side circuit-level trials (p≈10⁻³–3×10⁻³), reporting normalized logical error per logical qubit and overhead metrics for procurement and deployment decisions.

- Assumptions/dependencies: standardized reporting; fairness in circuit, decoder, and noise settings; block length vs hardware capacity trade-offs.

- Education and training materials for cyclic QEC layouts (sectors: education, workforce development)

- Develop course modules and interactive demos showing how cyclic symmetry reduces search space and how cyclic shifts enable constant-depth extraction.

- Tools: annotated Stim circuits; visualization of interleaved X/Z rounds and packed schedules.

- Assumptions/dependencies: access to open-source tooling; alignment with existing curricula in QEC.

Long-Term Applications

These applications require further research, scaling, or engineering development, particularly around logical gate sets, larger systems integration, and standardization.

- Universal fault-tolerant compute based on CxC codes (sectors: hardware, software, cloud QC)

- Extend from memory to gate-level fault tolerance: implement logical Clifford/T gates, lattice surgery, and transversal/gauge operations on C2/CxR codes; integrate methods cited for logical gates.

- Product/workflow: full-stack FT services (compile → layout → transport → decoding), leveraging cyclic layouts’ constant-depth advantages and robustness to hook errors.

- Assumptions/dependencies: validated logical gate constructions for CxC; hardware support for required multi-round operations; sustained decoder performance at scale; management of hook errors as per ongoing findings.

- Cross-architecture standardization of cyclic QEC (sectors: policy, standards, industry consortia)

- Develop standards for reporting circuit-level QEC performance, including cyclic shift capabilities, per-round depth, and normalized logical error per qubit.

- Policy/workflow: procurement guidelines for publicly funded systems requiring circuit-level evidence (vs code-capacity-only) and layout compatibility (2×n).

- Assumptions/dependencies: consensus among vendors/research labs; well-specified testbeds; access to reference code catalogs.

- Automated co-design of hardware transport primitives and cyclic code generators (sectors: robotics/control in quantum systems, hardware design)

- Co-optimize cyclic generator polynomials (weights and shifts) with physical transport capabilities (latency, error rates), possibly using reinforcement learning or combinatorial optimization guided by the cyclic symmetry constraints.

- Tools/products: co-design platforms that output both code parameters and transport schedules, optimizing for depth, throughput, and resilience to platform-specific errors.

- Assumptions/dependencies: rich hardware telemetry; accurate physical error models beyond depolarizing channels; sufficient computational resources for large co-design searches.

- Sector-specific quantum application enablement via improved logical error rates (sectors: healthcare, materials, energy, finance)

- With improved logical memory reliability, accelerate early FT demonstrations of algorithms (e.g., phase estimation, error-resilient VQE variants).

- Workflows/products: domain-specific pipelines using CxC-protected registers (e.g., chemistry simulation short circuits, secure key generation amplification).

- Assumptions/dependencies: availability of FT gate sets; integration of logical memory with algorithmic kernels; cost-performance acceptable at scale.

- Repository and ecosystem growth around cyclic-code-based LDPC QEC (sectors: academia, open-source)

- Maintain and expand public datasets of cyclic code seeds, HGP instances, performance curves, and layouts; foster cross-comparisons with BB codes and 2D-local LDPC layouts.

- Tools: open libraries for generator polynomial manipulation, compact layout synthesis, transport scheduling, and decoder tuning.

- Assumptions/dependencies: sustained community interest; permissive IP; contributions from hardware vendors to include platform-specific adapters.

- Resilience studies against hook errors and non-idealities (sectors: research, hardware validation)

- Systematically test CxC vs BB and other LDPC codes for hook error resilience; quantify impact on logical error under realistic scheduling and measurement conditions.

- Workflow: multi-platform trials with calibrated transport errors, measurement latency, asymmetric noise, and crosstalk models.

- Assumptions/dependencies: detailed platform models; cooperation across labs; alignment on metrics and benchmarks.

Key Assumptions and Dependencies Across Applications

- Hardware capabilities for cyclic shift operations, including opposite chiral motion for X/Z ancilla lanes, and reliable parallel gate execution.

- Noise rates and models close to the simulated depolarizing channels (p≈10⁻³), along with fast measurement/reset operations to maintain constant-depth schedules.

- Decoder performance and availability (BP+OSD or better) at the required block lengths and round counts; compute resources for real-time decoding.

- Trade-offs between stabilizer weight (≤10), block length (up to ~3200), and practical quantum hardware scale; choice of C2 (higher rate) vs CxR (lower weight).

- Standardized circuit-level benchmarking and transparent reporting to compare with BB and other LDPC codes in realistic settings.

Glossary

- Ancilla qubits: Auxiliary qubits used to extract syndrome information without disturbing data qubits. "The first row contains the data qubits and the second row contains the ancilla qubits."

- Bivariate bicycle (BB) codes: A quantum CSS code family built from bivariate circulant-based constructions, offering high performance and two-layer layouts. "A recent breakthrough is the discovery of bivariate bicycle (BB) codes which achieves better code parameters and logical error rate than surface codes and previous HGP codes, and can be implemented over two planar layers instead of four."

- Block length: The total number of physical qubits in the code. "The price to pay with HGP codes is a larger block length."

- BP+OSD: A decoder combining Belief Propagation with Ordered Statistics Decoding for improving decoding accuracy. "Our simulations were implemented in Stim and decoded using BP+OSD, instantiated for 10,000 BP iterations and 5-th order OSD."

- Circulant matrices: Special cyclic matrices where each row is a cyclic shift of the previous, often used as sparse building blocks. "Circulant matrices, , are special cyclic matrices of dimension , wherein iff , and is 0 otherwise."

- Circuit-level simulations: Simulations that model gate, measurement, and idle errors at the circuit operation level. "Circuit-level simulations show that they can achieve the same logical error rate as surface codes with a reduced qubit overhead."

- Code capacity model: A simplified noise model assessing code performance without full circuit details. "The main limitation of that approach is that the code capacity model is too simplistic and it does not guarantee good performance in practice."

- Code capacity simulations: Simulations under the code capacity model to estimate logical performance. "The HGP codes of~\cite{grospellier2021combining, tremblay2022constant} were obtained by generating hundreds of random HGP codes and selecting the one achieving the lowest logical error rate for a specific noise rate with code capacity simulations."

- Code rate: The ratio of logical qubits to physical qubits in a code. "The CxR code then has block length , code rate , minimum distance , and check weights ."

- CSS codes: A class of stabilizer codes with separate X- and Z-type parity checks enabling simpler decoding. "{\em CSS codes} are stabilizer codes where the set of stabilizer generators can be partitioned into and types, whose only non-trivial Pauli operators are and respectively."

- Cyclic HGP codes: Hypergraph product codes built from two cyclic codes, imposing global symmetry. "Namely, we consider {\em cyclic HGP codes} that are the product of two cyclic codes and that we call CxC codes."

- Cyclic layout: A hardware arrangement leveraging cyclic shifts to align ancilla and data qubits efficiently. "we argue that our CxC codes admit convenient implementation under a {\em cyclic layout}, constructed via ideas we previously described in~\cite{Tham2025}."

- Cyclic matrices: Sparse binary matrices whose entries are determined by a cyclic generating function. "A common building block for classical and quantum binary codes are sparse {\em cyclic matrices} , which are binary matrices with the form ."

- Cyclic shift: A hardware-supported operation that cyclically translates qubits/ancillae to achieve alignment. "The cyclic shift lets us align the ancilla qubits with the data qubits they need to interact with."

- C2 codes: Symmetric cyclic HGP codes formed as the hypergraph product of a cyclic code with itself. "we study C2 codes which are the product a cyclic code with itself"

- CxC codes: Cyclic hypergraph product codes defined as the HGP of two cyclic codes. "In other words, a CxC code is the hypergraph product of two cyclic codes."

- CxR codes: Cyclic HGP codes formed as the hypergraph product of a cyclic code with a repetition code. "and CxR codes which are the product of a cyclic codes with a repetition code."

- Data qubits: Qubits that carry the encoded logical information. "The first row contains the data qubits and the second row contains the ancilla qubits."

- Depolarizing channels: Noise models that apply random Pauli errors after operations with specified probability. "are followed by one- or two-qubit depolarizing channels (whichever is appropriate for the operation) with noise rate ."

- Encoding overhead: The inverse of code rate, measuring how many physical qubits per logical qubit. "\Cref{fig:sym-cHGP} shows a comparison of distance vs encoding overhead (inverse of code rate) for several C2 instances"

- Encoding rate: The fraction of physical qubits that encode logical information; synonymous with code rate. "Unlike surface codes, quantum LDPC codes can achieve a constant encoding rate and a growing minimum distance."

- Flying qubits: Qubits that can be physically transported (e.g., ions, photons) to enable long-range interactions. "quantum computing platforms with flying qubits capable of implementing a cyclic shift such as photonic qubits"

- HGP construction: The hypergraph product method for building quantum LDPC codes from classical codes. "Tillich and Zémor proposed the HGP construction producing the first family of quantum LDPC codes with constant encoding rate and polynomial minimum distance"

- Hook errors: Correlated faults caused by multi-qubit operations that can degrade code distance. "The advantage of HGP codes might reside in their robustness against hook errors"

- Hyper-bicycle codes: A generalization related to HGP codes using sums of tensor products with circulants. "hyper-bicycle codes were introduced, which are in fact HGP codes, wherein and are sums of tensor products of arbitrary binary matrices with permutations of circulant matrices."

- Hypergraph product (HGP) codes: Quantum LDPC codes constructed via the hypergraph product of classical codes. "Hypergraph product (HGP) codes are one of the most popular family of quantum low-density parity-check (LDPC) codes."

- Logical error rate: The probability that a logical qubit suffers an error after encoding and decoding. "Circuit-level simulations show that they can achieve the same logical error rate as surface codes with a reduced qubit overhead."

- Logical error rate per logical qubit: Logical error probability normalized per encoded logical qubit. "achieving better parameters and a logical error rate per logical qubit that is up to three orders of magnitude better."

- Minimum distance: The smallest weight of a logical operator or undetectable error; governs error suppression scaling. "Unlike surface codes, quantum LDPC codes can achieve a constant encoding rate and a growing minimum distance."

- Parity check matrices: Binary matrices specifying stabilizer generators’ support for CSS codes. "it is convenient to organize them into rows of parity check matrices "

- Progressive edge growth: A classical code construction heuristic that avoids harmful local structures. "the progressive edge growth algorithm produces high performing classical codes by eliminating local patterns, such as the so-called trapping set that degrade decoder performance."

- QCCD architecture: Quantum CCD-style architecture arranging qubits in a 2×n array with constrained movement. "we design an efficient planar layout for the QCCD architecture, allowing for a trapped ion implementation of the syndrome extraction circuit in constant depth."

- Quantum error-correction (QEC): Techniques to protect quantum information from noise using redundancy and measurements. "Constructing a large-scale quantum computer requires the use of quantum error-correction (QEC) to keep errors in check."

- Quantum LDPC codes: Quantum codes with sparse parity checks, enabling scalable rates and distances. "Unlike surface codes, quantum LDPC codes can achieve a constant encoding rate and a growing minimum distance."

- Repetition code: A simple classical/quantum code that repeats bits/qubits to detect errors; used as a seed in CxR. "which are the product of a cyclic codes with a repetition code."

- Stabilizer codes: Quantum codes defined by a commuting group of Pauli operators (the stabilizer) whose +1 eigenspace encodes information. "{\em Stabilizer codes} are QEC codes whose check operators are elements of a {\em stabilizer group}, ."

- Stabilizer generators: The minimal set of commuting Pauli checks generating the stabilizer group. "That group's {\em stabilizer generators}, , in turn are a set of mutually commuting Pauli operators"

- Surface codes: Topological quantum codes on 2D lattices, widely used as a baseline for performance comparisons. "Unlike surface codes, quantum LDPC codes can achieve a constant encoding rate and a growing minimum distance."

- Syndrome extraction circuit: The measurement circuit that gathers check outcomes to detect and correct errors. "allowing for a trapped ion implementation of the syndrome extraction circuit in constant depth."

- Tensor product: A mathematical operation combining matrices/operators; used to build HGP and hyper-bicycle constructions. "sums of tensor products of arbitrary binary matrices with permutations of circulant matrices."

- Toric code: A specific topological code (a surface code on a torus) obtainable as a special case of CxC. "Notably, the standard toric code is obtainable by setting and , and ."

- Trapping set: A local structure in Tanner graphs that can mislead decoders and harm performance. "such as the so-called trapping set that degrade decoder performance."

- Two-block construction: A CSS code construction from two compatible classical codes arranged in block form. "CSS codes may be constructed by elevating two compatible classical codes through the two-block construction."

Collections

Sign up for free to add this paper to one or more collections.