- The paper demonstrates integration of volatile STM and non-volatile LTM switching in CVD-grown MoS₂ memristors, achieving 89.56% accuracy on digit recognition.

- It employs precise material synthesis and device fabrication, with Raman, PL, and HRSTEM analyses verifying uniformity and tunable analog conductance.

- The reservoir framework achieves picojoule energy efficiency and robust non-linear time-series prediction, underscoring its potential for neuromorphic hardware.

Interfacial and Bulk Switching MoS₂ Memristors for All-2D Reservoir Computing Framework

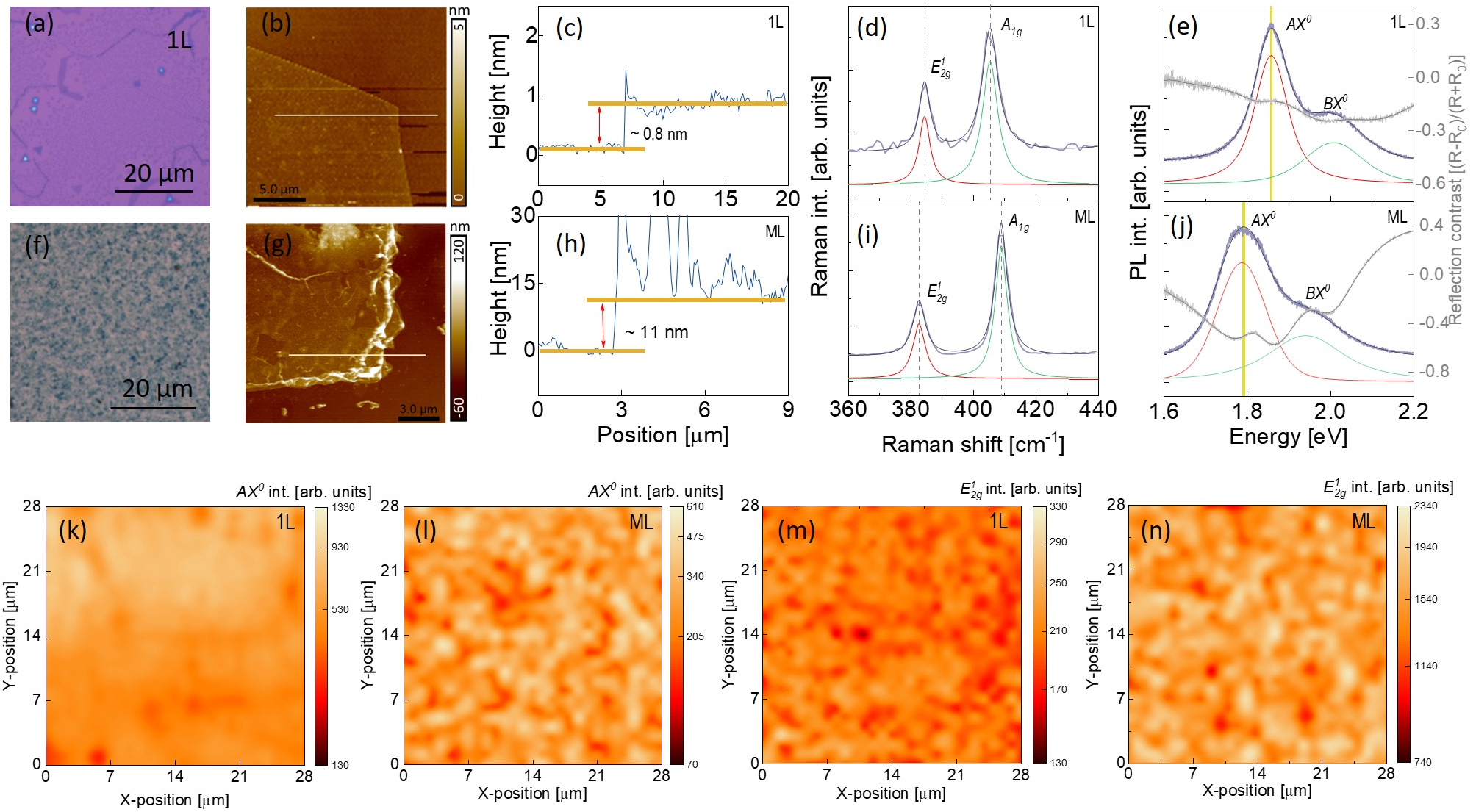

Materials Synthesis and Characterization

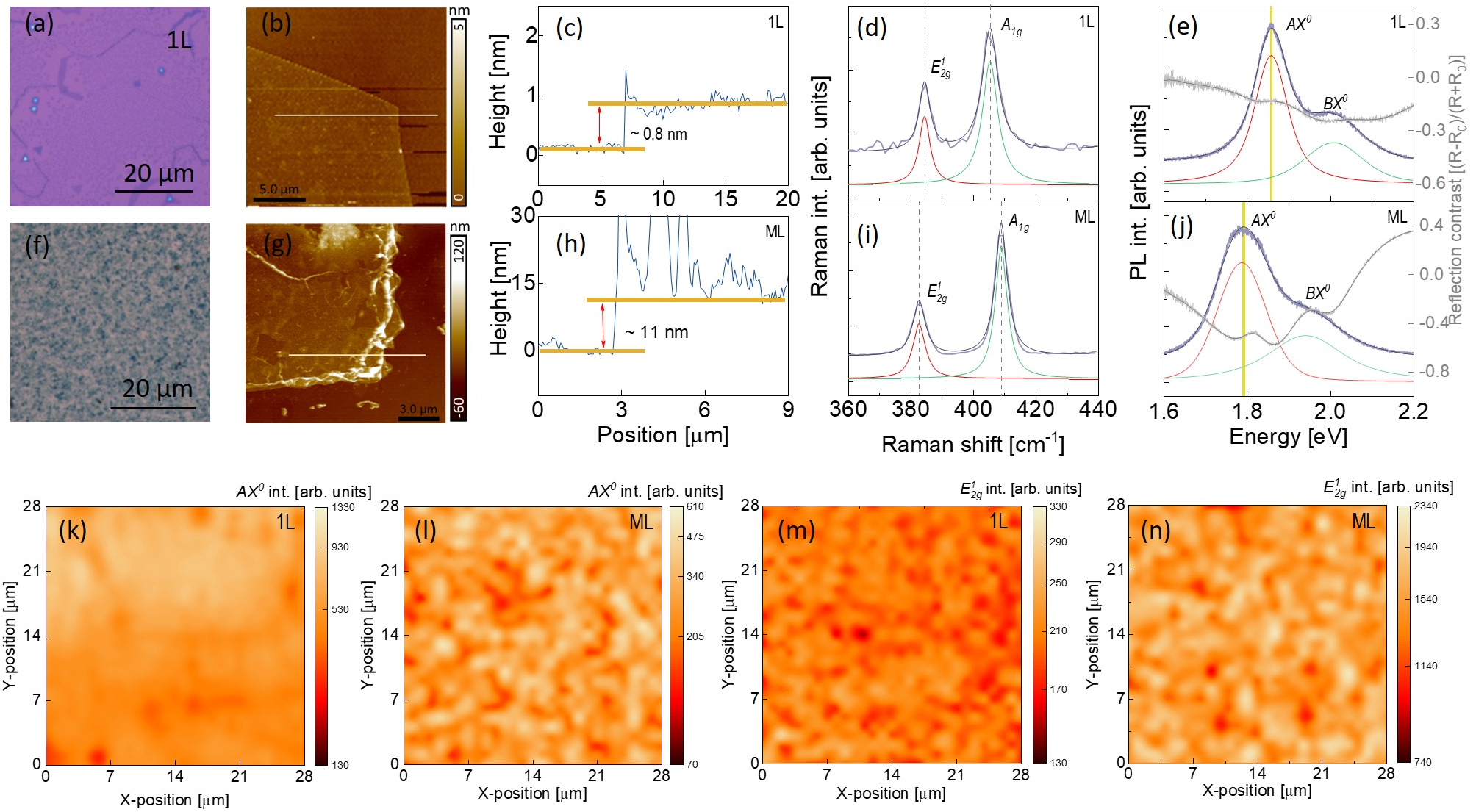

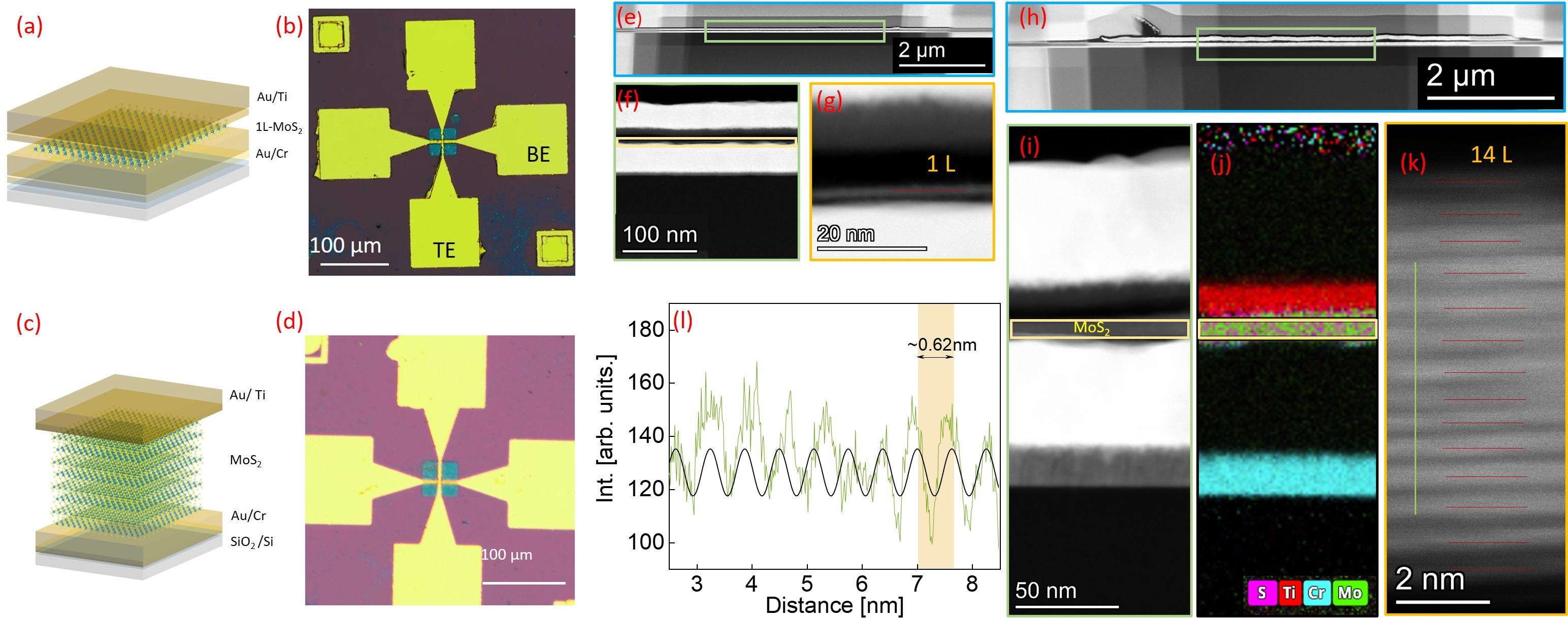

This work demonstrates the integration of short-term and long-term memory (STM/LTM) memristors based on monolayer (1L) and multilayer (ML) MoS₂, respectively, fabricated via large-area chemical vapor deposition (CVD). The physical and chemical uniformity of both film types was verified using optical and atomic force microscopy (AFM), Raman spectroscopy, and photoluminescence (PL), confirming atomically flat surfaces and consistent thickness for monolayer (~0.8 nm) and multilayer (~11 nm, 14 layers) samples. Raman shifts and PL peak ratios corroborated material quality and layer count, with negligible sample variability across mapped regions.

Figure 1: Morphological, spectroscopic, and mapping analyses establishing atomic-scale uniformity of CVD-grown monolayer and multilayer MoS₂ films.

Device Fabrication and Transport Mechanisms

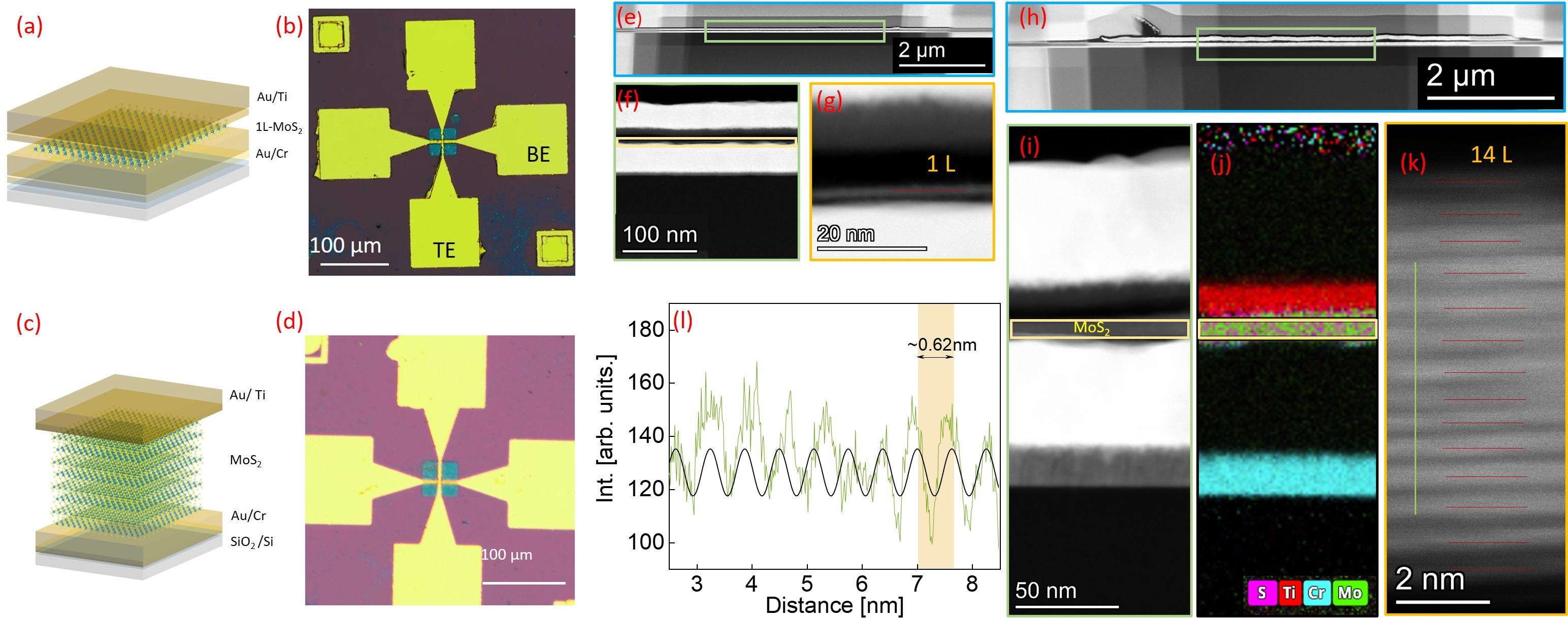

Memristive crossbar arrays with two-terminal Au/Ti/MoS₂/Au stacks were constructed, with both monolayer and multilayer devices assessed. High-resolution scanning transmission electron microscopy (HRSTEM) confirmed the structural integrity of MoS₂ layers and the absence of significant electrode interdiffusion in pristine samples.

Figure 2: Schematic and HRSTEM validation of fabricated 1L and ML-MoS₂ memristive devices and interface periodicity.

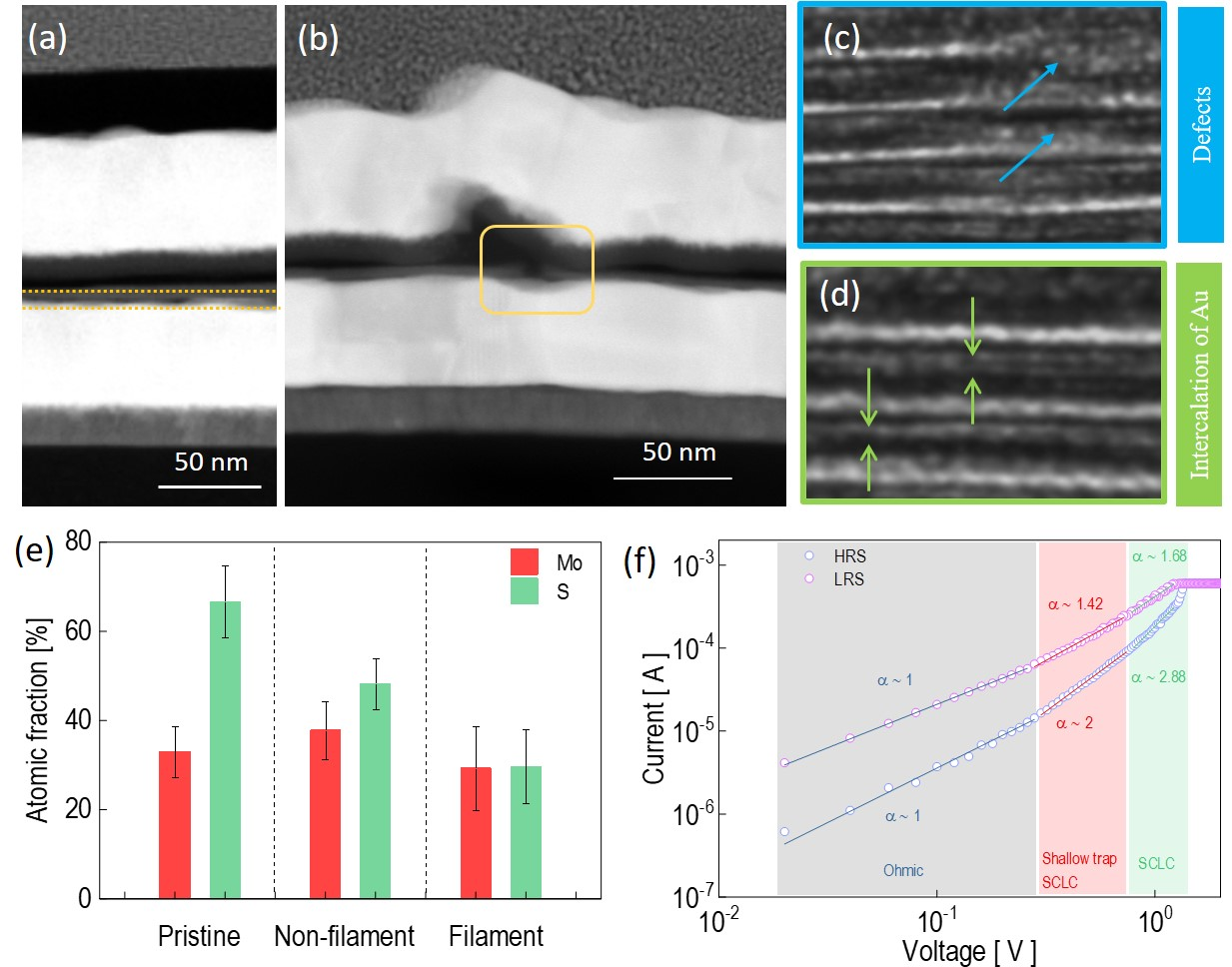

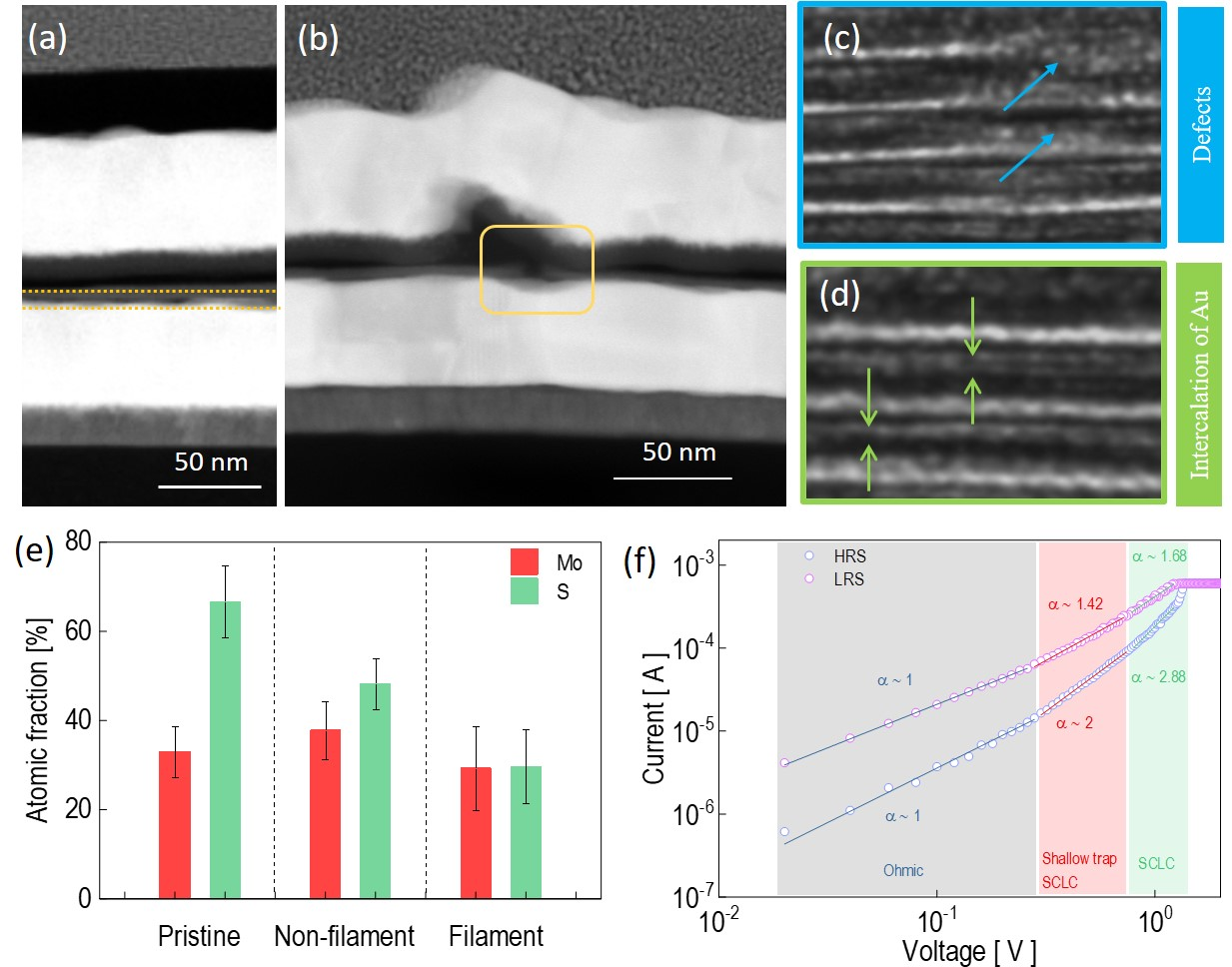

Electrical characterization revealed that 1L-MoS₂ devices exhibit volatile STM switching without requiring electroforming; the observed dynamics result primarily from Schottky barrier modulation at the Ti/MoS₂ interface. In contrast, ML-MoS₂ devices display non-volatile LTM switching with a pronounced analog conductance response, necessitating an initial electroforming step that provokes S-vacancy filament formation and subsequent bulk-limited trap-assisted space charge limited conduction (SCLC). Post-switching HRSTEM and EDS identified regions with reduced S content and Au intercalation, confirming filamentary and bulk-defect mechanisms.

Figure 3: HRSTEM and EDS evidence of conductive filament formation and non-filament region defects post electroforming; transport fitted to SCLC.

Analog Synaptic Arrays and STM Reservoir Dynamics

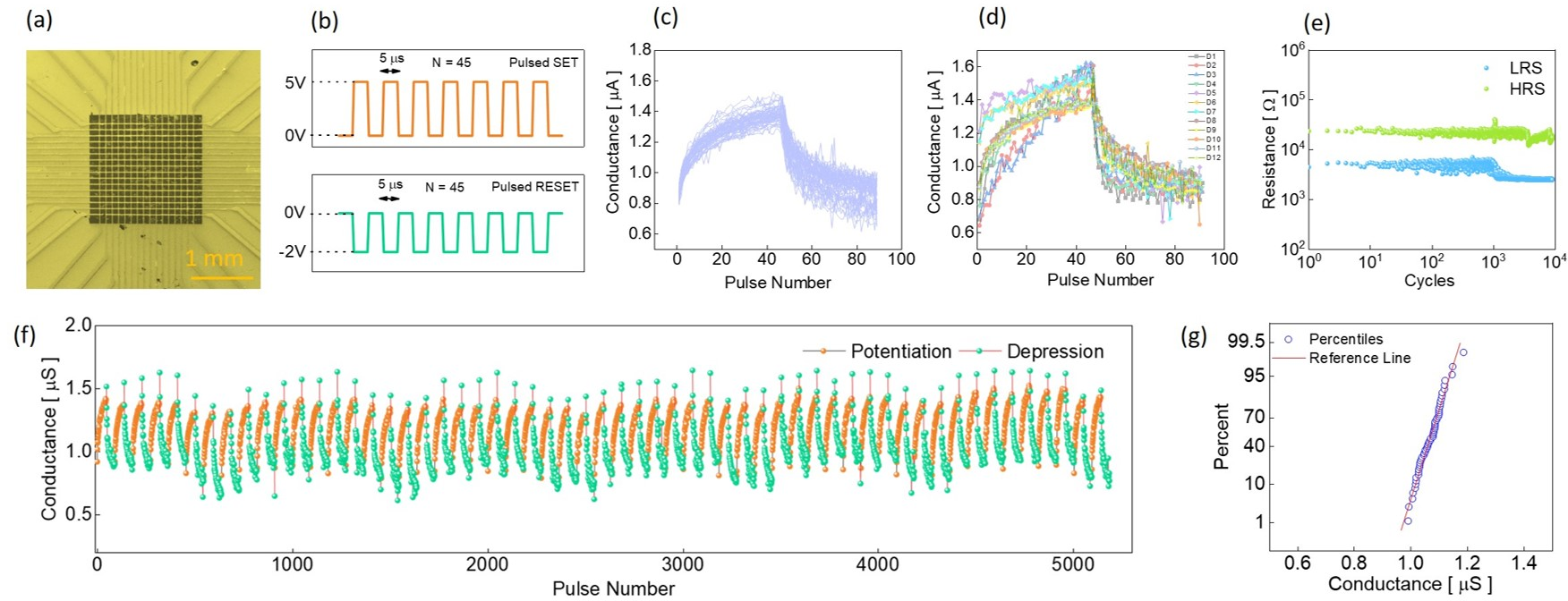

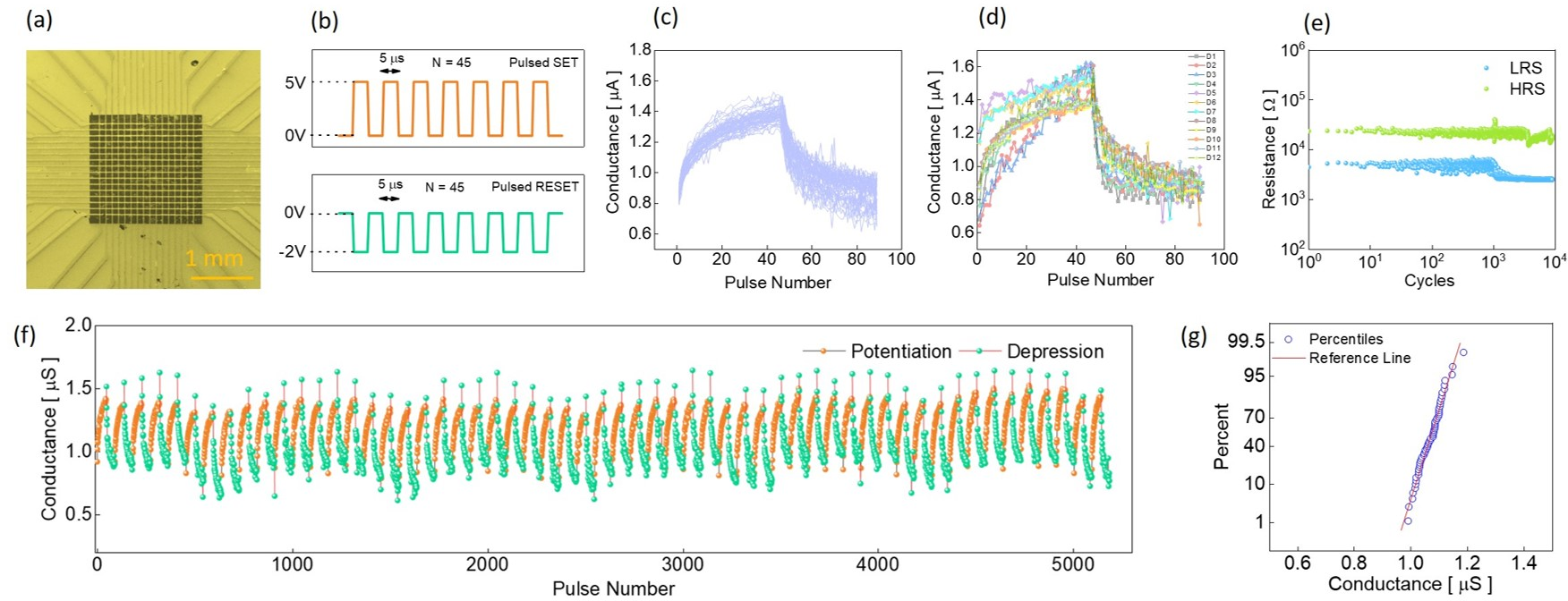

The ML-MoS₂ crossbar arrays (16x16) demonstrated exceptional analog conductance tunability, with robust endurance (up to 10,000 cycles) and cycle-to-cycle (C2C) standard error below 4%. This tunability, including gradual potentiation/depression (P/D), represents a critical improvement over filamentary memristor variability prevalent in oxide-based devices.

Figure 4: SEM micrograph, pulse programming, endurance, and statistics affirming uniform analog behavior of ML-MoS₂ arrays.

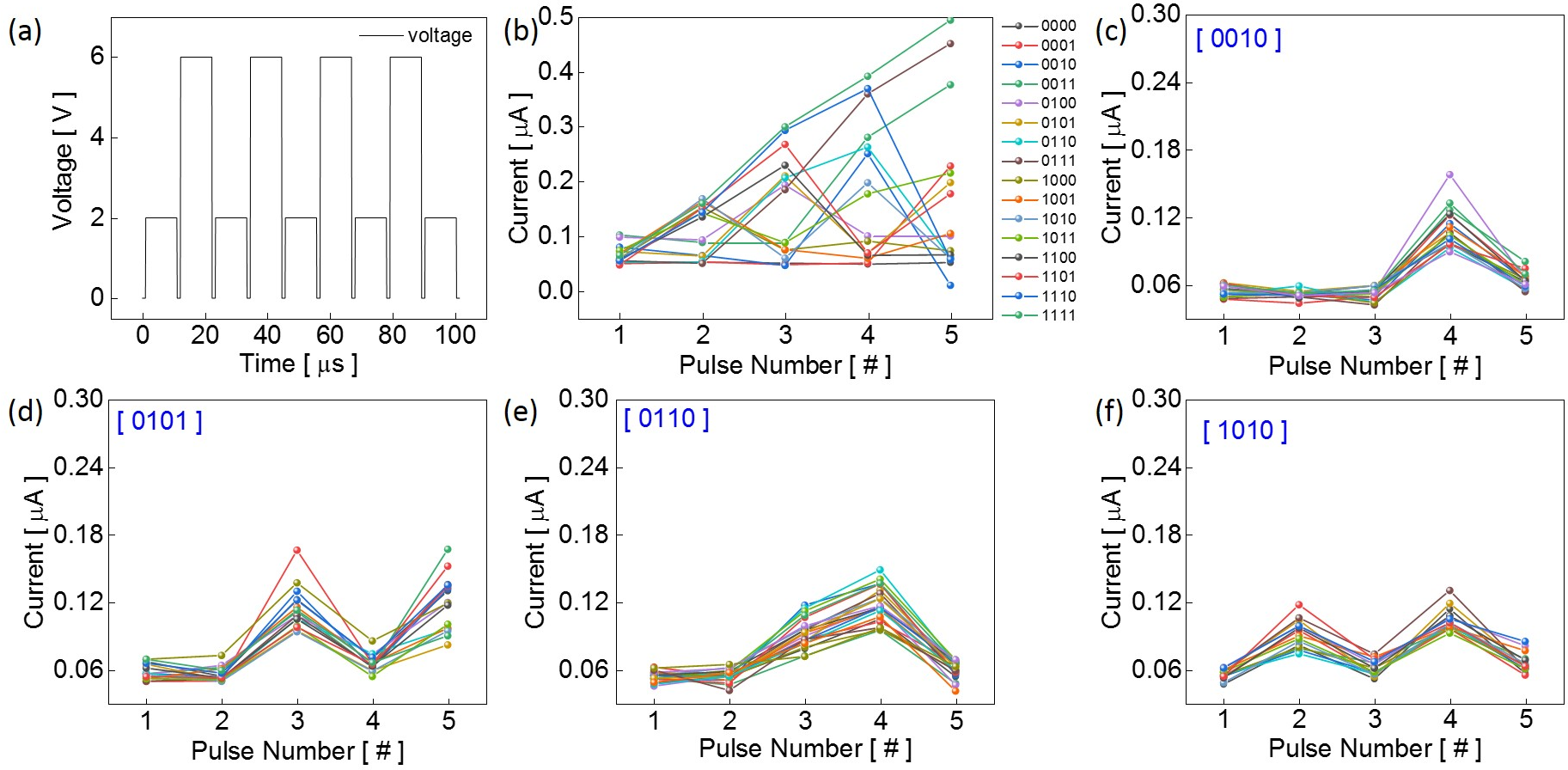

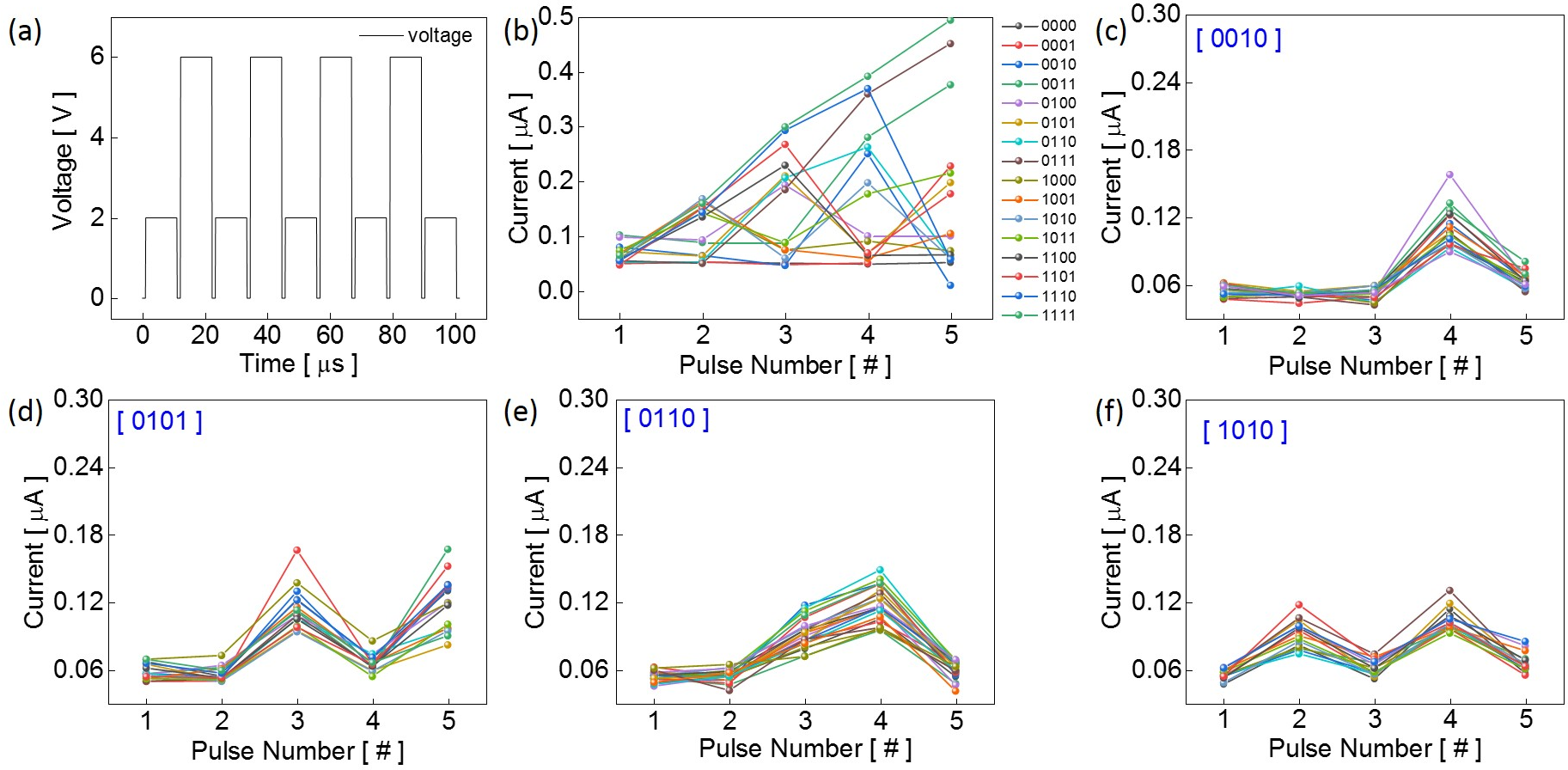

For STM modeling, the 1L-MoS₂ devices were configured to produce 4-bit states, yielding 16 distinctly addressable output levels. Repeated cycling confirmed low C2C variability and precise state encoding, instrumental for hardware reservoir neurons.

Figure 5: Pulse stream protocol and measured output states demonstrating volatile, repeatable STM encoding for reservoir nodes.

Memristive Reservoir Computing Framework

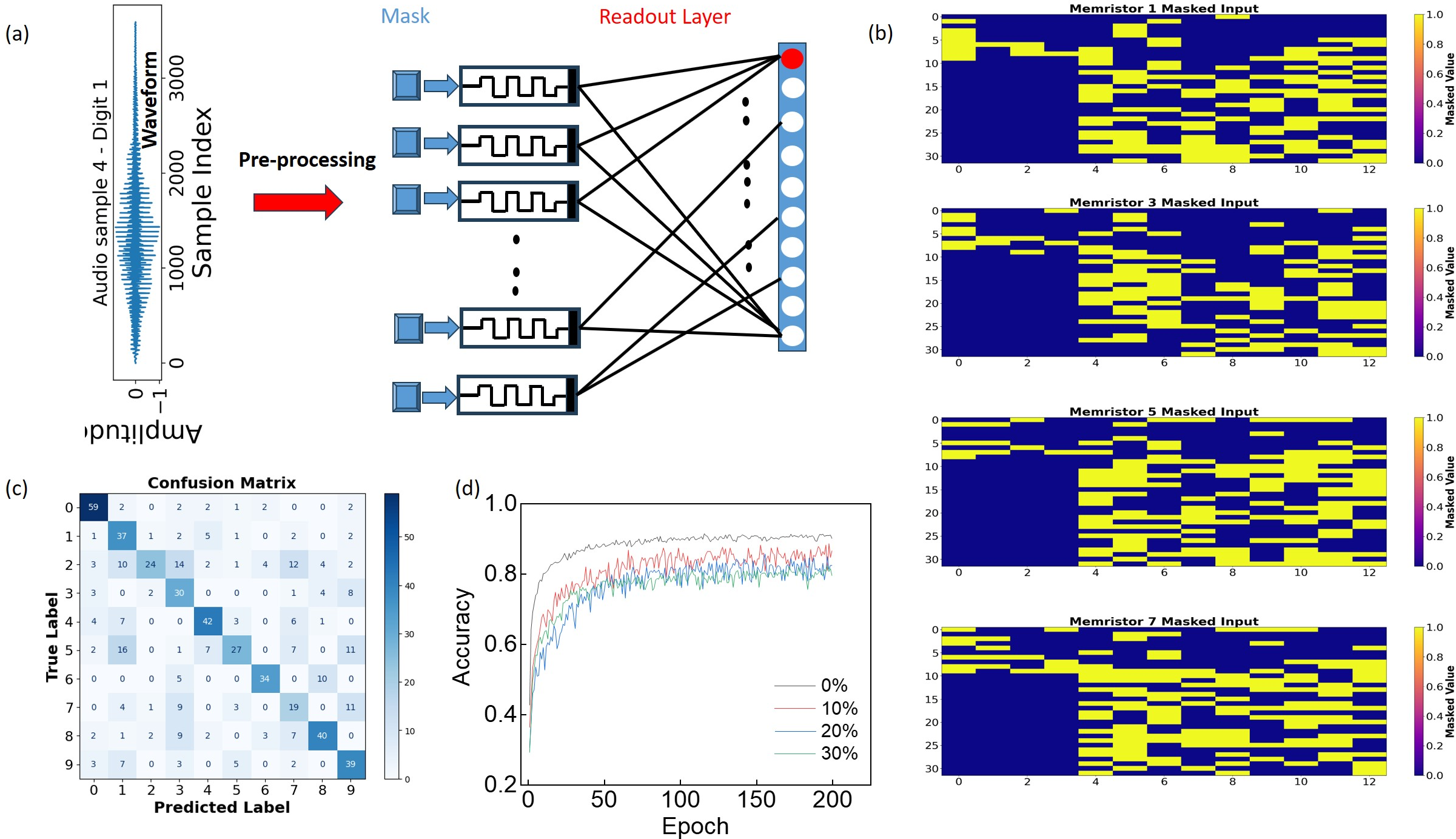

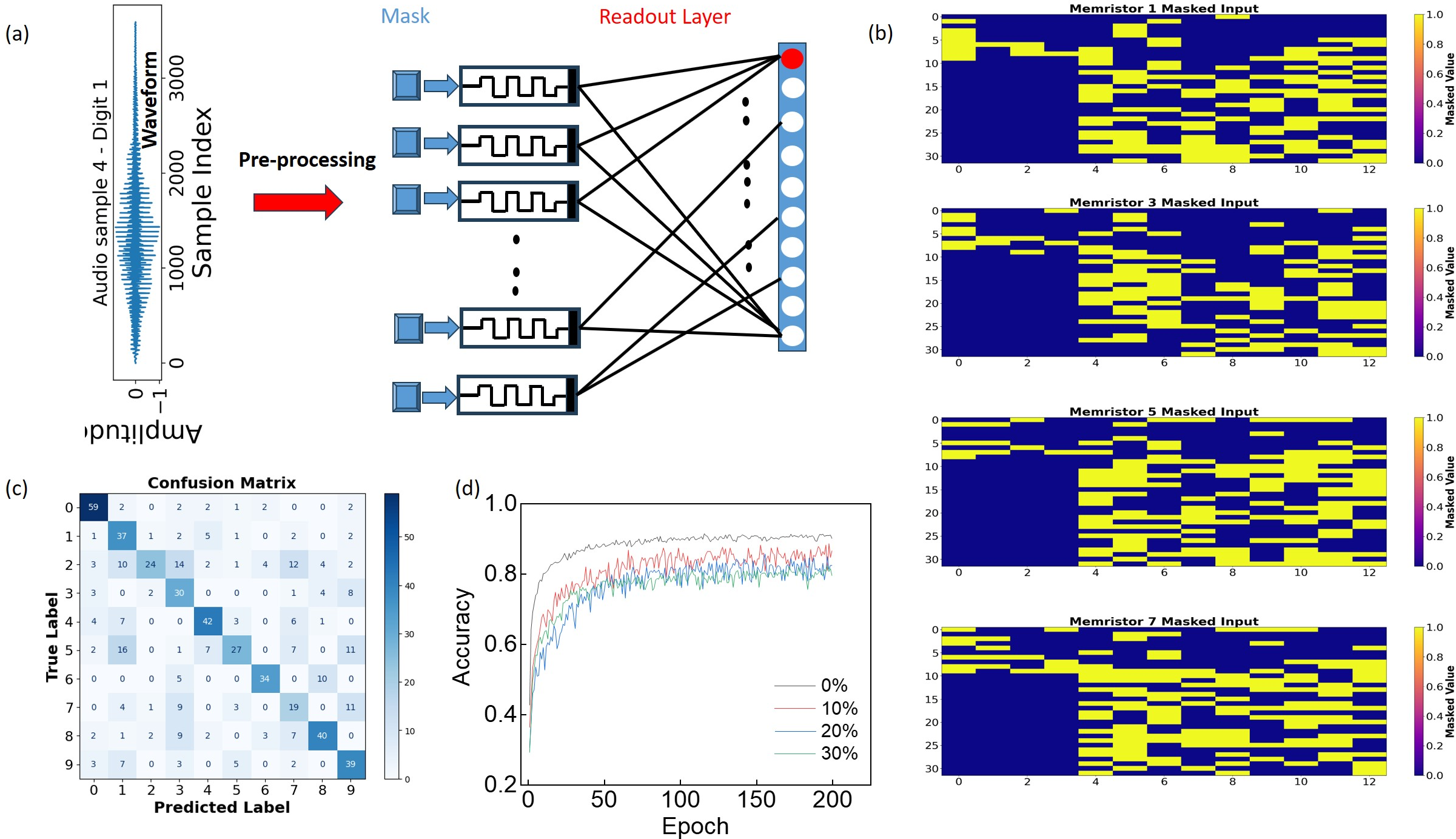

The integrated framework leverages the volatile STM dynamics of 1L-MoS₂ memristors as reservoir nodes and the long-term stable ML-MoS₂ arrays as analog synapses for the readout layer. On the spoken digit recognition task (using the Free Spoken Digit Dataset), audio data is processed into MFCC features, encoded into bit streams, and mapped to device current states. The readout layer is trained via Manhattan update rule and device-inspired noise models. Reported precision is 89.56%, with a word error rate (WER) near 0.145%; simulation confirms robust performance under input noise perturbations.

Figure 6: Reservoir computing architecture for spoken digit recognition; accuracy and confusion metrics for memristor-driven framework.

Nonlinear Time-Series Prediction

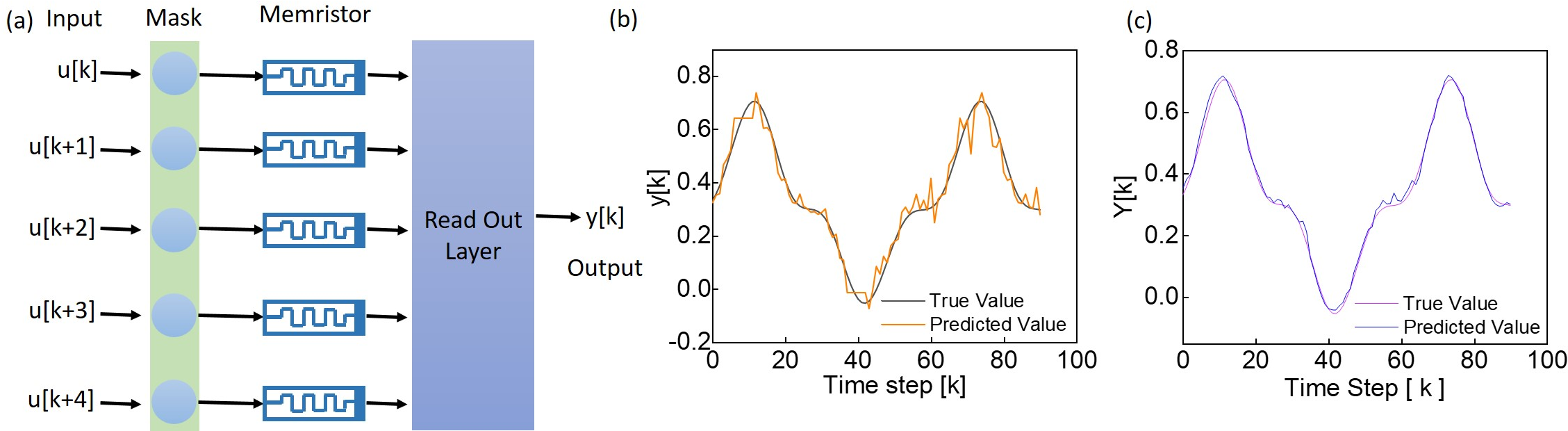

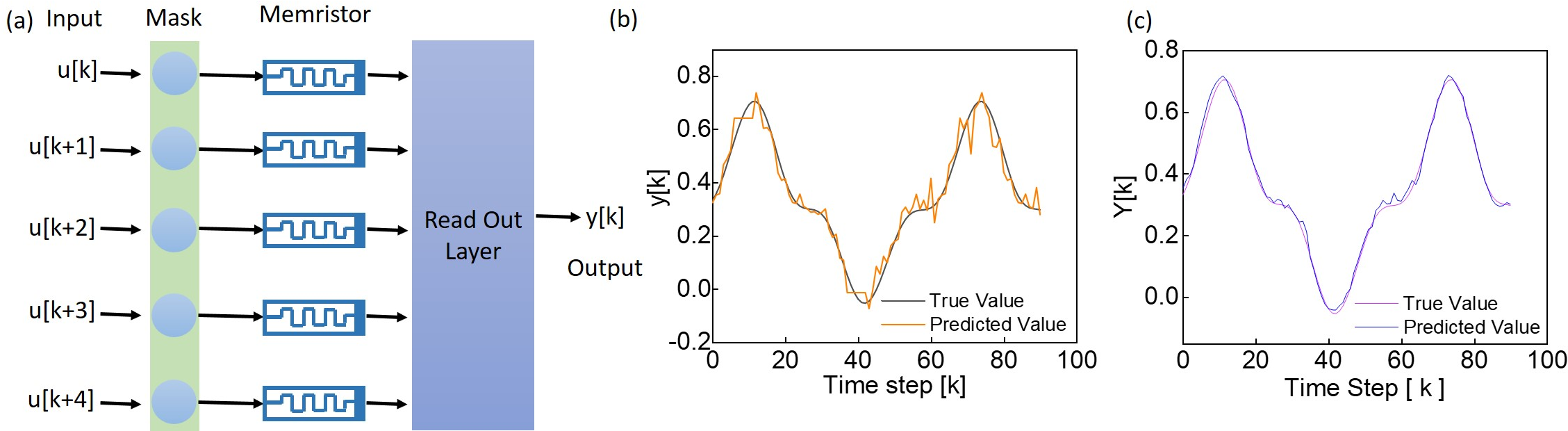

The same architecture was tested on nonlinear dynamic equation prediction: y[k]=0.1y[k−1]+0.2y[k−2]y[k−3]+0.3u[k]3+0.25. Inputs were mapped to the physical devices; the readout layer modeled as a two-layer neural network (128/64 neurons). Both offline and online learning protocols enabled accurate prediction with near-perfect correlation of true vs. predicted outputs.

Figure 7: Memristor-based framework for nonlinear time-series prediction; offline and online learning performance.

Energy Efficiency and Hardware Prospects

The system achieves energy consumption in the picojoule range per operation, primarily limited by ADC requirements for input mapping. Training operation counts and network efficiency compare favorably with state-of-the-art memristive RC implementations, with up to 181.8 million OPS/W for the digit recognition task. The analog synaptic arrays offer a pathway to highly scalable low-power neuromorphic hardware.

Conclusion

The paper presents a comprehensive study of CVD-grown monolayer and multilayer MoS₂ memristors for reservoir computing. Novel integration of volatile and nonvolatile switching mechanisms enables robust, low-variability hardware modeling of STM and LTM required for reservoir and readout layers. The demonstrated framework achieves competitive accuracy on spoken digit recognition and time-series forecasting, with energy efficiency and scalability validated by extensive hardware characterization. The results position non-filamentary, all-2D memristor architectures as promising candidates for future analog AI accelerators and adaptive temporal information processing systems (2511.16557).