- The paper presents a novel approach using iceberg and concatenated codes to encode many logical qubits, experimentally surpassing break-even error rates.

- It details efficient fault-tolerant protocols including GHZ-based state preparation and parallel syndrome extraction that reduce logical infidelity compared to unencoded circuits.

- Application-level benchmarks in quantum simulation highlight the method’s resource efficiency and practical error suppression for near-term quantum computing.

Computing with Many Encoded Logical Qubits Beyond Break-Even: A Technical Analysis

Introduction

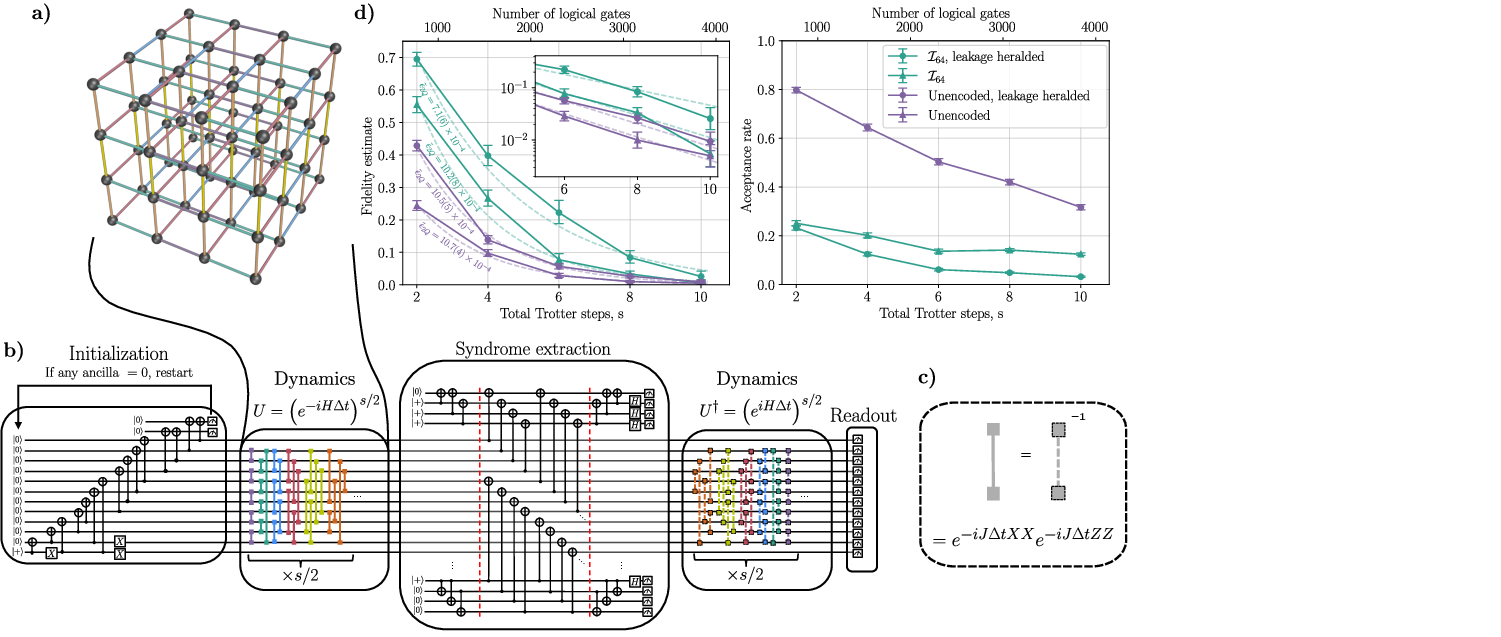

This work realizes scalable, high-rate quantum error correction and detection using novel encoded logical qubits implemented on a 98-qubit trapped-ion quantum processor. By leveraging the exceptional connectivity and coherence properties of the Quantinuum Helios platform, the authors demonstrate that encoded logical circuits can outperform their best unencoded analogs. Specifically, the development and concatenation of iceberg codes provide efficient, high-rate logical encodings with practical gadgets for initialization, syndrome extraction, gate benchmarking, and quantum simulation applications.

The study showcases both fully fault-tolerant (FT) and partially fault-tolerant (pFT) protocols, including up to 94 logical qubits with iceberg quantum error-detecting (QED) codes and up to 48 logical qubits with two-level concatenated quantum error-correcting (QEC) codes. The clear surpassing of the break-even point in experimental benchmarks represents a decisive step in both resource efficiency and error suppression for near-term quantum computing.

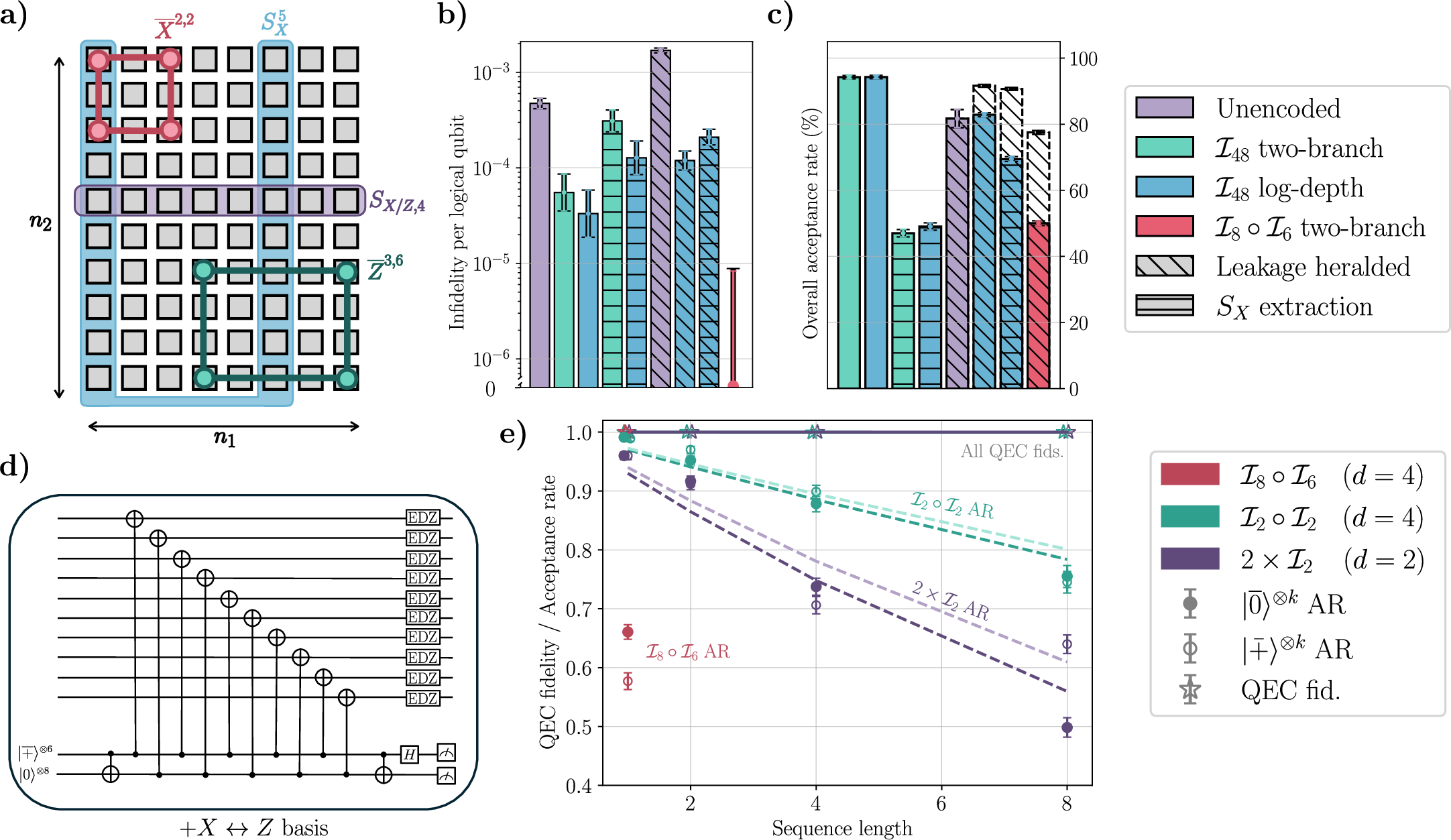

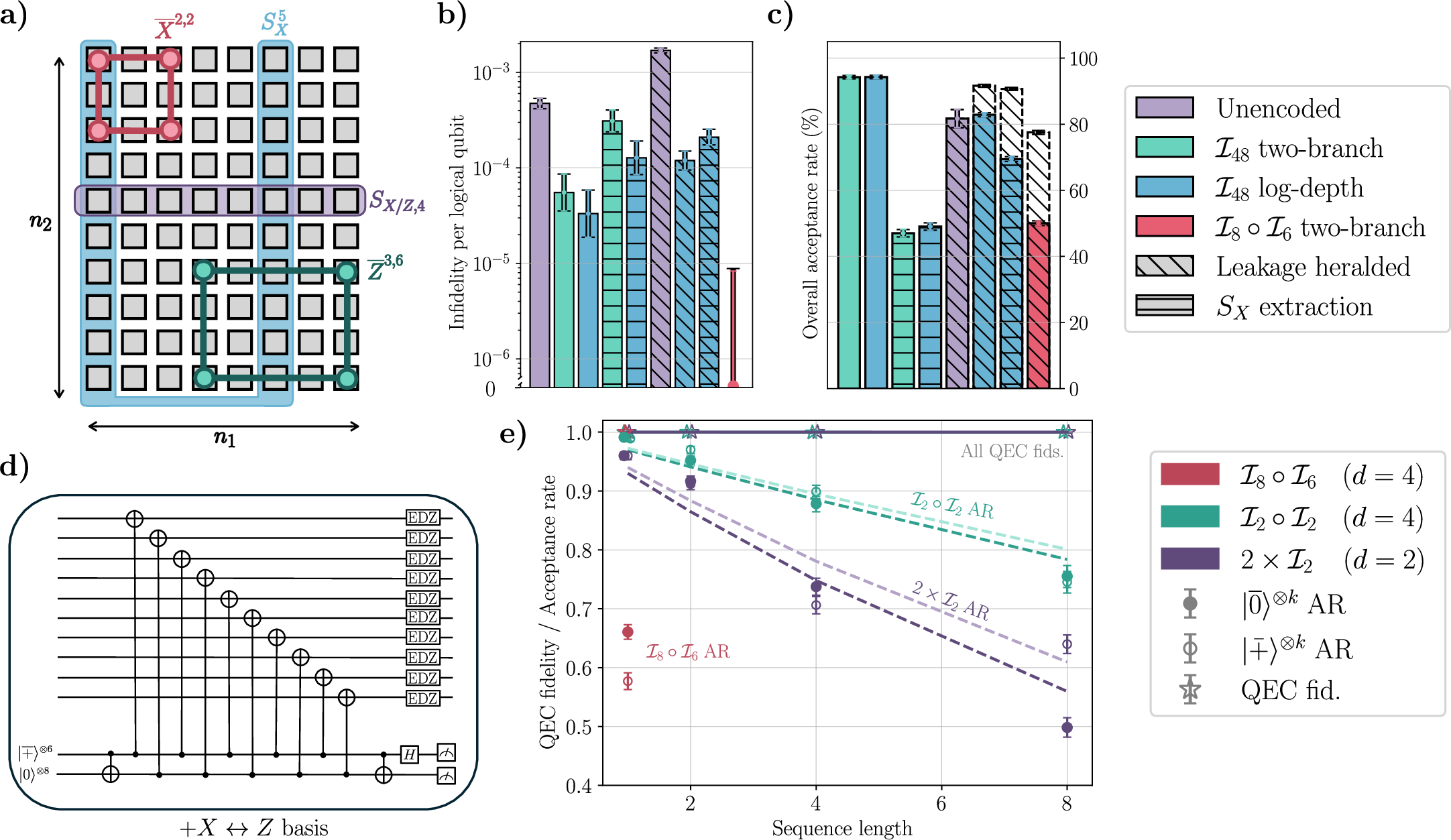

Iceberg Codes and Concatenation

The iceberg code family, parameterized as I{k}, encodes k logical qubits into n=k+2 physical qubits at code distance 2. The codes are stabilized globally by SX=∏j=0n−1Xj and SZ=∏j=0n−1Zj, allowing any even-weight Pauli strings as logical operators. Concatenation, denoted I{k2}∘I{k1}, extends the code distance multiplicatively and achieves high rates, encoding k1k2 logical qubits at distance d1d2 with n1n2 physical qubits. The layout and stabilizer structure are readily visualized and support efficient parallelized syndrome extraction.

Figure 1: Iceberg codes and their concatenation: grid layout and performance data for various code configurations, showcasing logical infidelity and acceptance rates in SPAM and QEC benchmarking.

Code concatenation enables the systematic increase of code distance, and the architecture supports variable block sizes for both QED (d=2) and QEC (d=4). This flexibility is crucial for balancing shot overhead, acceptance rates, and resource allocation in experimental practice.

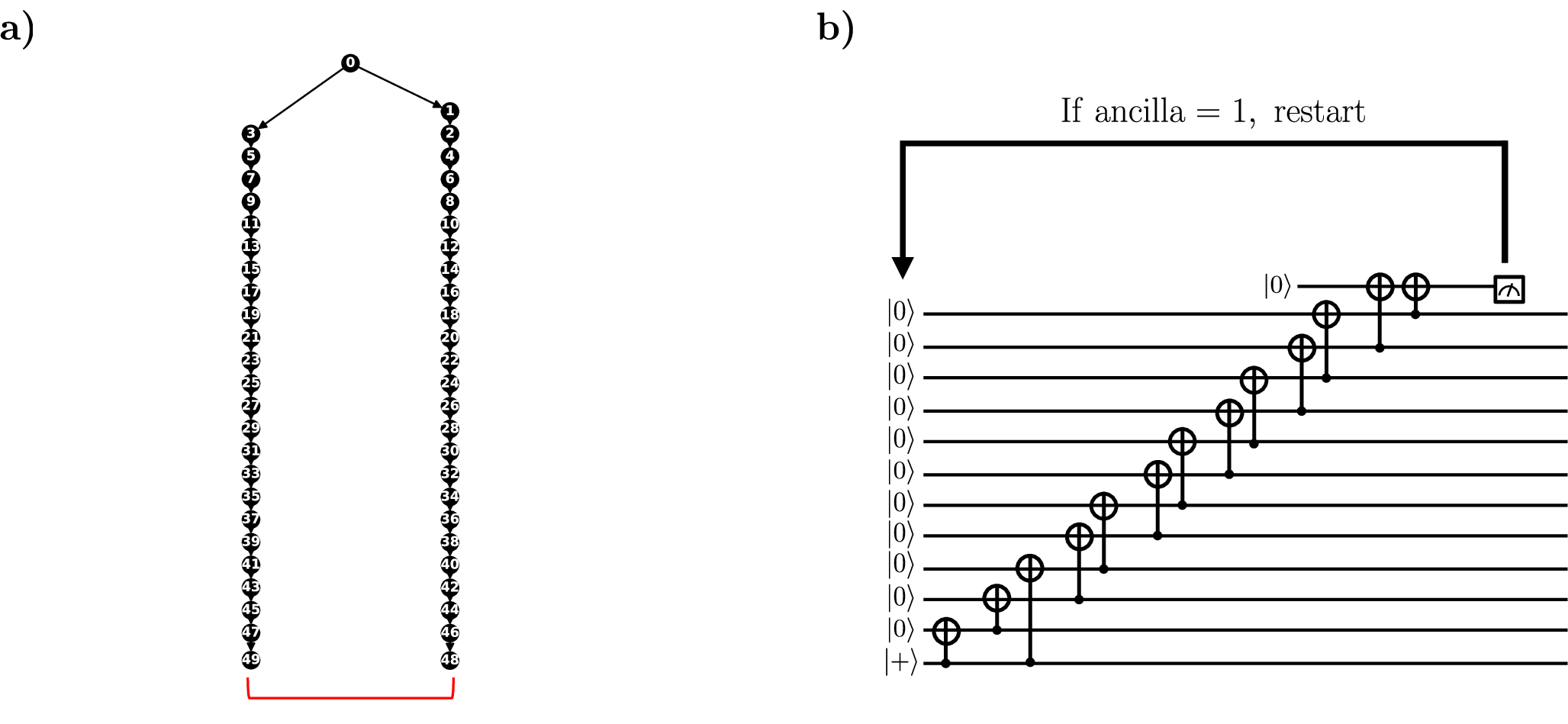

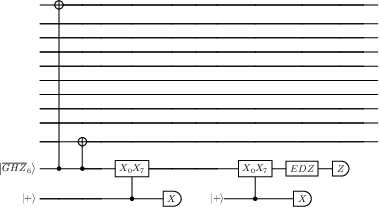

Fault-Tolerant State Preparation, Syndrome Extraction, and Decoding

The paper introduces log-depth and branch-based gadgets for FT state preparation using GHZ-like circuits. Key features include:

Syndrome extraction is implemented through parallelized GHZ-based ancilla strategies that match the native parallelism of Helios hardware (8 gate zones). Circuit-level decoding employs a hierarchy of stabilizer measurements and flag qubits, ensuring the detection and correction of both weight-1 and generalized weight-2 errors. For d=4 concatenated codes, a new QEC cycle is described, and its decoder is proven to meet FT ExRec conditions under circuit-level noise.

Figure 3: Circuit-level decoding flow for the d=4 concatenated iceberg QEC cycle, showing propagation and correction.

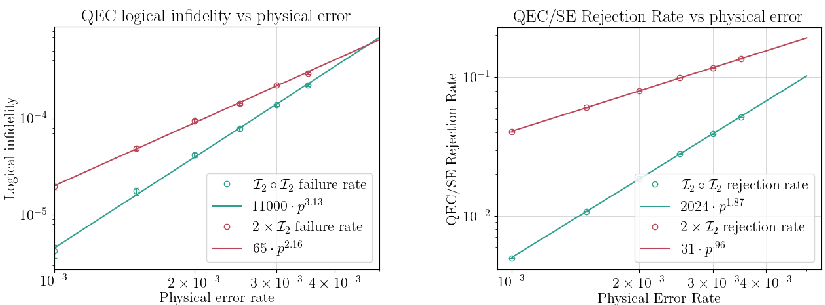

Strong numerical results are presented, with the logical QEC infidelity per cycle per qubit in a $48$-qubit I{8}∘I{6} code upper-bounded at 4×10−5—an order-of-magnitude improvement over the best unencoded equivalents.

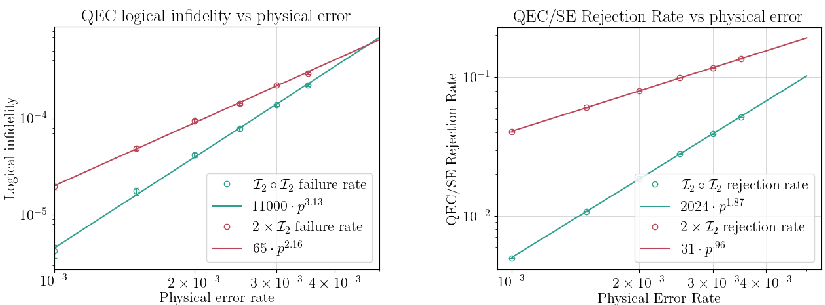

Figure 4: Simulated QEC infidelity and reject rate scaling as a function of physical gate error, illustrating distance-2 vs. distance-4 performance.

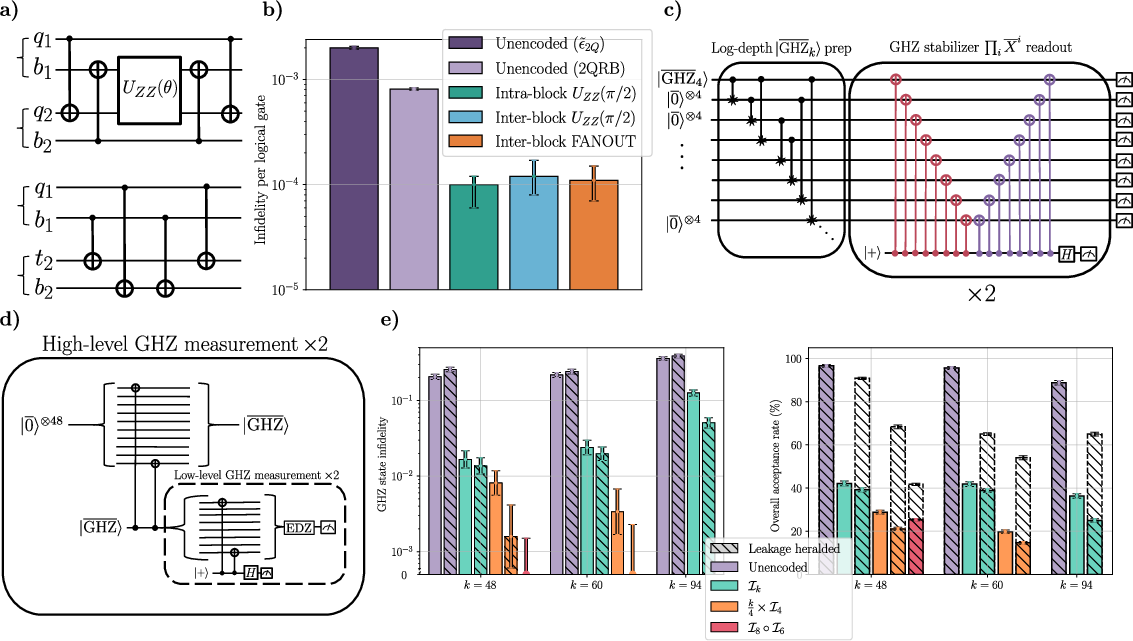

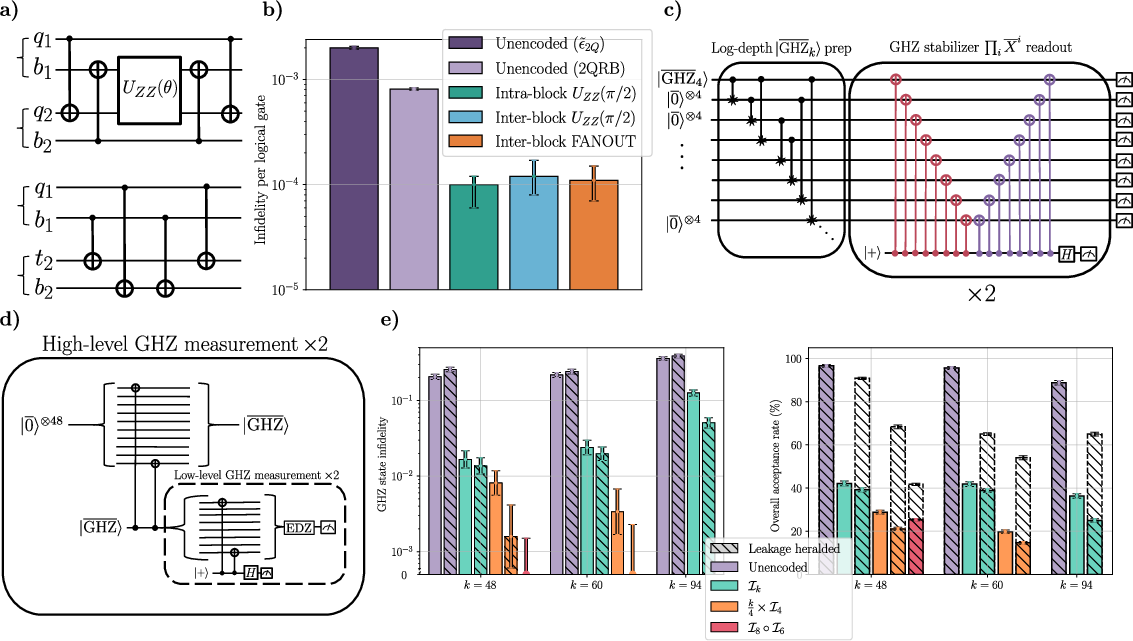

Logical Gate Benchmarking and Entangled State Preparation

The authors implement logical Clifford and Pauli gates, including intra/inter-block UZZ(θ) rotations and a fully FT FANOUT gate, using a logical version of cycle benchmarking (CB) with syndrome extraction rounds interleaved every 8 gates. Crucially, logical gate infidelities (e.g., $1.0$–1.2×10−4 for UZZ(π/2) and FANOUT) are all substantially below the lowest measured physical two-qubit gate errors on the hardware (≈8×10−4–2×10−3).

Figure 5: Logical gate benchmarking and GHZ state preparation protocols, with reported infidelities and acceptance rates for both unencoded and encoded scenarios.

GHZ state preparation is achieved for states of 48–94 logical qubits with postselection only on FT-allowed syndromes, reaching logical state fidelities up to $0.986$ (I{48}), $0.998$ (I{60}, I{4} blocks), and with no detected logical error over thousands of shots at d=4. The GHZ state preparation protocol is proven FT up to O(p3) logical error scaling.

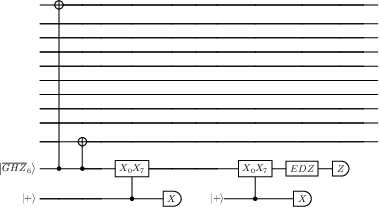

Figure 6: Fault-tolerant protocol for measuring the global logical X stabilizer during encoded GHZ state preparation.

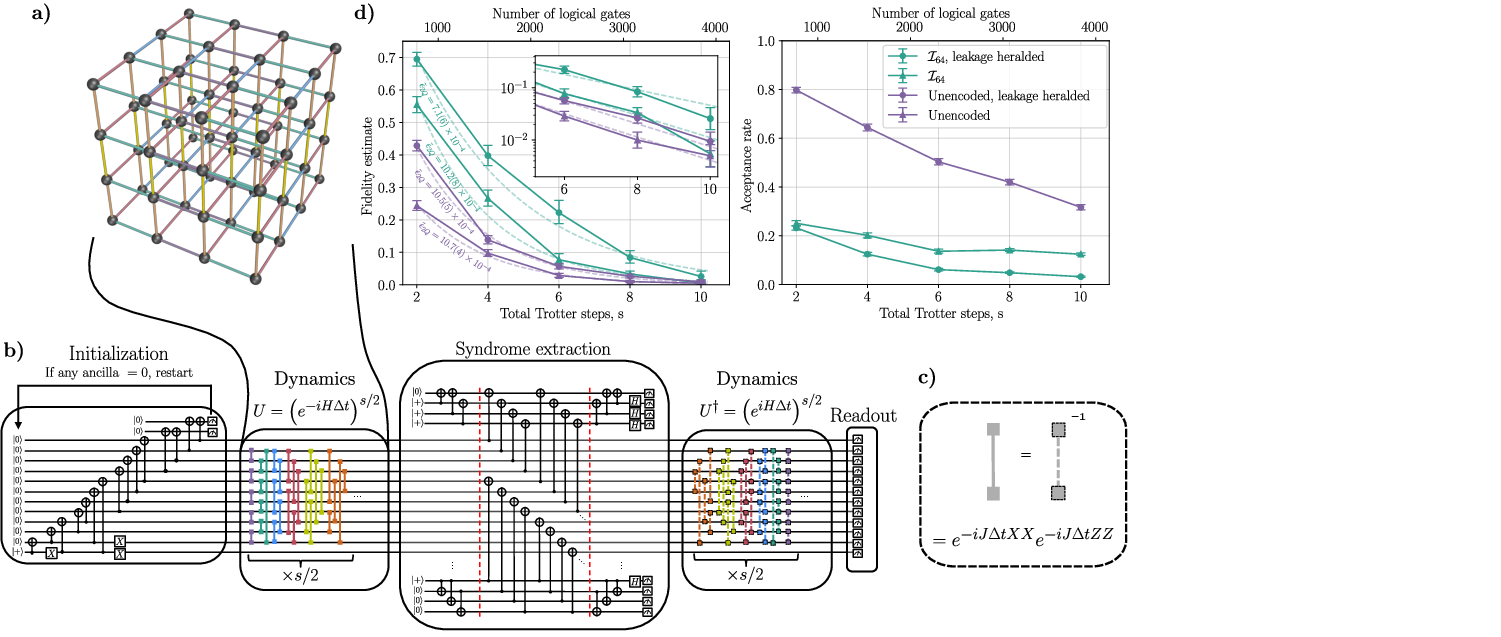

Application-Level Benchmarks: Quantum Simulation

To probe the practical relevance of encoded computation, the paper executes a large-scale mirror benchmarking (MB) protocol for a Trotterized evolution of a $3$D XY model (on a 4×4×4 lattice, k=64 logical qubits) using the I{64} code. All gates and measurements are carried out at the encoded logical level with syndrome extraction and error-detection postselection. Acceptance rates remain practical for substantial circuit depths (across 10 Trotter steps, >3%), and the effective per-logical-gate error (ϵ~2Q) is reduced by approximately 30% with iceberg encoding compared to unencoded circuits.

Figure 7: Mirror benchmarking of encoded Hamiltonian simulation, with fidelity and acceptance versus Trotterization steps.

These results approach the classical simulation boundary, as forward time-evolution circuits of this scale and entanglement are challenging for tensor network or exact methods. The implementation highlights the importance of bias-tailored errors and hardware-efficient code design.

Alternative Preparation and Decoding Techniques

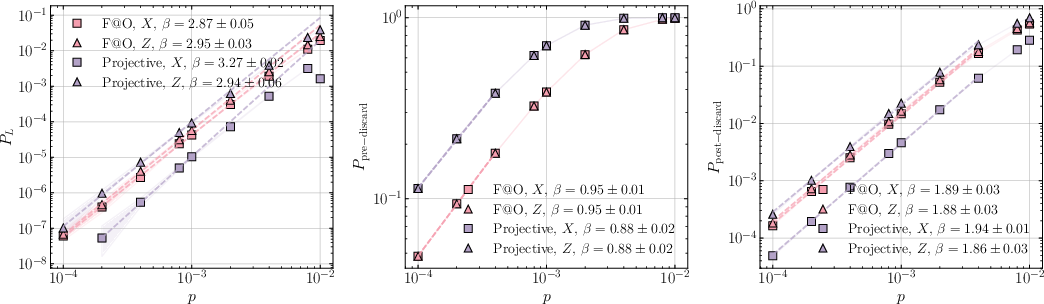

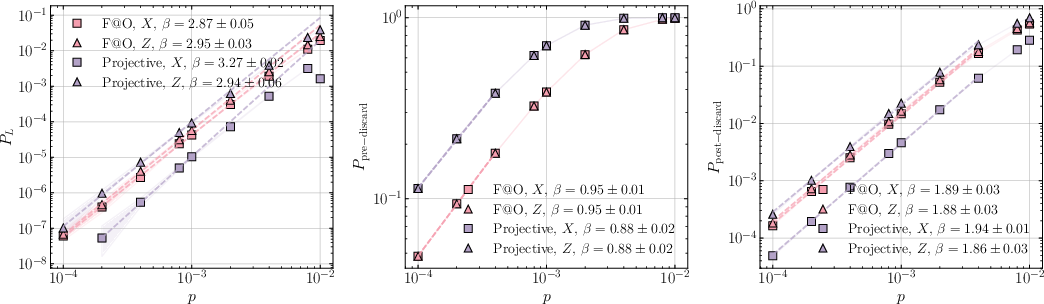

The authors further analyze alternative FT resource state preparation strategies—projective, flag-at-origin, and flag-based (ILP-generated circuit) methods. These are benchmarked by simulation for logical error, pre-acceptance, and post-acceptance rates, revealing that even general-purpose FT approaches can realize O(p3) logical error scaling at d=4, though method choice affects resource and time overhead.

Figure 8: Performance of logical state preparation for a random CSS product state under several FT methods and postselection regimes.

Hierarchical and look-up table based decoding strategies are considered, exploiting the concatenated structure for further error suppression and highlighting future architectures for scalable decoding pipelines.

Implications, Limitations, and Future Directions

The results substantiate the practical viability of high-rate, all-to-all quantum codes for both near-term and scalable quantum computation. Three main implications arise:

- Resource Efficiency and Error Suppression: The use of high-rate codes, coupled with circuit-level-FT gadgets and efficient syndrome extraction, pushes logical error rates well below unencoded benchmarks at no unwieldy physical overhead.

- Beyond Break-Even in Application Context: Encoded logical circuits, including complex application-level quantum simulation tasks, can now outpace the best realizable unencoded computations in both fidelity and depth.

- Near-Term Pathways to Full Fault Tolerance: While pFT techniques suffice for many near-term applications, the experimentally realized code concatenation and FT gadgets demonstrate a clear method to further suppress both logical error and postselection overhead in tandem with hardware improvements.

Theoretically, the work suggests that code families such as iceberg and concatenated many-hypercube codes may offer an optimal compromise between rate, decoding complexity, and gadget efficiency compared to toric- or surface-based schemes in modular hardware with high connectivity.

On the practical side, the demonstrated protocols are highly compatible with the all-to-all native connectivity in both trapped-ion and neutral-atom platforms. Extensions to application-motivated non-Clifford resource state preparation, logical magic state distillation, and FT surface code-logic modules integrated via automorphisms or modular gadgets are evident directions.

Challenges remain in minimizing postselection for fully scalable applications, implementing real-time FT feedback, and integrating classical decoders. However, with measured logical error and acceptance rates in the correct asymptotic regimes, the field is positioned for further escalation in both code distance and native logical gate set diversity.

Conclusion

This work presents a comprehensive, experimentally backed framework for high-rate, concatenated quantum codes achieving logical error suppression beyond the unencoded device limits. The modularity and efficiency of the iceberg code family, combined with the native capabilities of the Quantinuum Helios platform, establishes new benchmarks for logical qubit performance, paving the way to larger-scale fault-tolerant quantum computation and beyond-classical quantum simulations in the near term.