- The paper introduces the LLM-USO framework that blends large language models with Bayesian Optimization to optimize analog circuit design and enable knowledge reuse.

- It employs structured design knowledge representation, integrating domain insights from previous circuits to guide the optimization process.

- Experimental results show improved circuit performance and efficiency, achieving optimal design points with fewer iterations than traditional methods.

LLM-USO: LLM-based Universal Sizing Optimizer

Abstract

The paper "LLM-USO: LLM-based Universal Sizing Optimizer" introduces an innovative framework aimed at optimizing analog circuit design by effectively integrating LLMs with traditional Bayesian Optimization (BO) techniques. This approach highlights significant advancements over existing methods by addressing limitations such as the lack of semantic understanding in traditional BO and the inability of such methods to reuse optimization knowledge across different circuit designs.

Introduction

Analog circuit design is a fundamental yet complex task in the field of integrated circuit (IC) development. The process demands balancing multiple objectives, such as power efficiency, area optimization, and performance fidelity, necessitating a high degree of expertise. Traditional approaches, such as BO, offer a systematic method for exploring large design spaces but often lack the domain-specific insights that seasoned human designers apply. The recent incorporation of machine learning, particularly LLMs, has shown promise in bridging this gap by providing an enriched understanding of domain knowledge, albeit with limitations like repetitive suggestions and poor leverage of prior context from similar designs.

Methodology

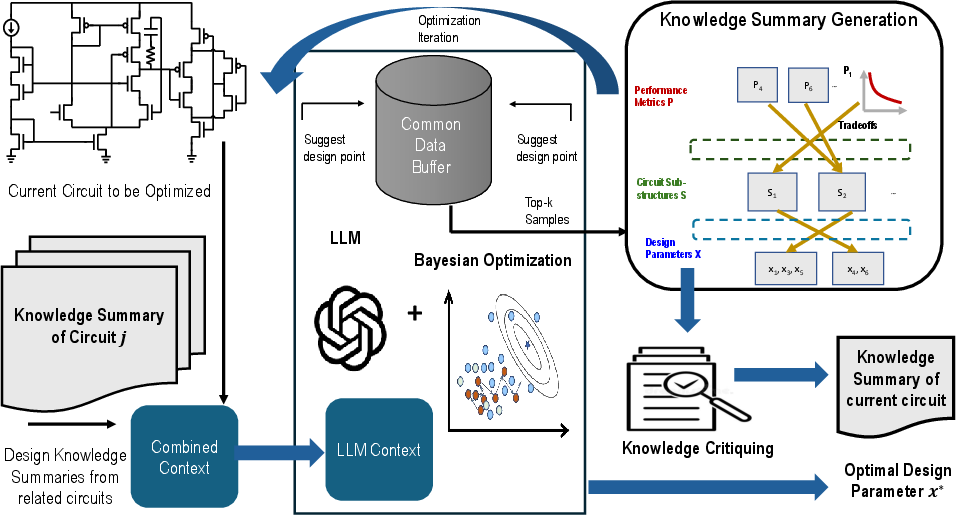

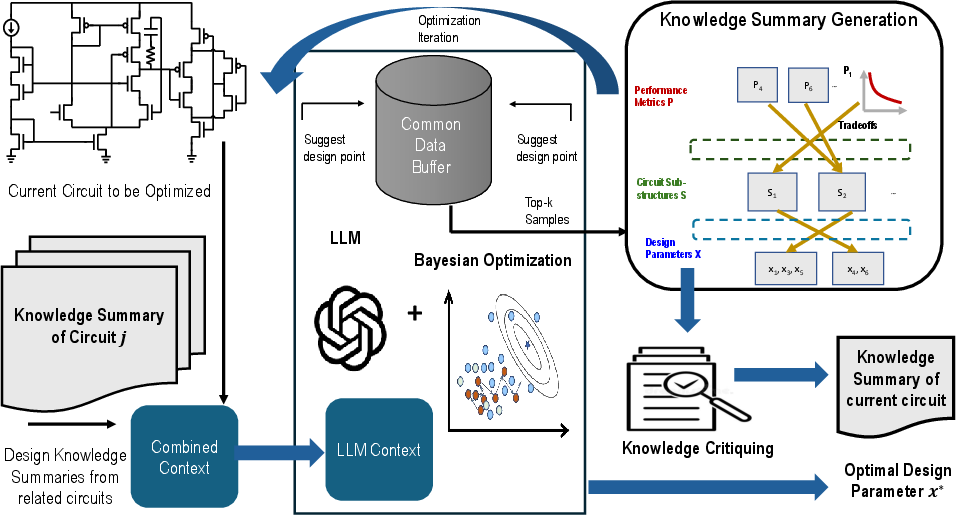

Figure 1: LLM-USO: Employs structured design knowledge summaries from related circuits for the optimization of the current circuit. LLM-USO generated the optimal design point $x^*$ and also the knowledge summary for the given circuit.

The core contribution of the paper is the development of the LLM-USO framework, which systematically encodes circuit design knowledge into a structured text format. This enables the reuse of optimization insights across circuits with similar sub-structures, thus mimicking the cognitive strategies employed by expert designers. The comprehensive methodology includes:

- Knowledge Representation: Analog circuit design knowledge is represented in a structured format capturing interactions between performance metrics, sub-structures, and design parameters.

- Hybrid Framework: The integration of BO with LLMs allows for the infusion of domain-specific knowledge into the optimization process and facilitates knowledge transfer, thus enhancing the efficiency and effectiveness of design exploration.

- Knowledge Summary Mechanism: A process to distill and apply design insights from one circuit to others, along with a critiquing mechanism to ensure summary accuracy and quality. This utilizes a structured prompt design and examples from previous optimizations for demonstration.

- Uncertainty-Based Ranking: LLM suggestions are ranked using BO's uncertainty estimates, prioritizing unexplored, high-potential design points.

Experiments and Evaluation

Extensive evaluations were conducted using transfer learning experiments on various analog circuits, demonstrating how LLM-USO significantly improves circuit design optimization quality. This was tested against traditional methods like standalone BO and prior frameworks such as ADO-LLM.

- Performance Gains: LLM-USO showed substantial improvements in achieving circuit specifications, often with fewer iterations and less computational overhead compared to traditional BO methods.

- Efficiency through Reuse: By leveraging design insights from previously optimized circuits, LLM-USO significantly reduced the time needed to reach optimal design points, particularly in complex circuit architectures.

Conclusion

The LLM-USO framework presents a substantial advancement in the field of electronic design automation, facilitating more efficient and effective analog circuit design optimization. By introducing structured knowledge representation and leveraging LLMs within a BO framework, it provides the dual benefit of improved design performance and enhanced transfer learning capabilities. This work sets a valuable precedent for future research in applying AI to complex engineering problems, emphasizing the critical role of information reuse and domain-specific knowledge integration.